### bookboon.com

### **CMOS Integrated Circuit Simulation: Solutions**

Erik Bruun

Download free books at

bookboon.com

### **ERIK BRUUN**

## CMOS INTEGRATED CIRCUIT SIMULATION SOLUTIONS

CMOS Integrated Circuit Simulation: Solutions

1<sup>st</sup> edition

© 2016 Erik Bruun & bookboon.com

ISBN 978-87-403-1339-0

Peer reviewed by Ivan H.H. Jørgensen, Associate Professor, Technical University of Denmark

### **CONTENTS**

| Preface                                             | 5   |

|-----------------------------------------------------|-----|

| Introduction                                        | 6   |

| Tutorial 1 – Resistive Circuits                     | 9   |

| Tutorial 2 – Circuits with Capacitors and Inductors | 21  |

| Tutorial 3 – MOS Transistors                        | 29  |

| Tutorial 4 – Basic Gain Stages                      | 43  |

| Tutorial 5 – Hierarchical Design                    | 71  |

| Tutorial 6 – Process and Parameter Variations       | 83  |

| Tutorial 7 – Importing and Exporting Files          | 99  |

| Appendix A – Errata                                 | 105 |

Rand Merchant Bank uses good business to create a better world, which is one of the reasons that the country's top talent chooses to work at RMB. For more information visit us at www.rmb.co.za

Thinking that can change your world

### **Preface**

This book contains the end-of-chapter problems for each of the tutorials in the book 'CMOS Integrated Circuit Simulation with LTspice IV – a Tutorial Guide' (1<sup>st</sup> edition, 2015, also published by Bookboon) and provides solutions to the problems. For each of the problems, corresponding LTspice schematics are shown together with the simulation outputs resulting from running the simulation specified in the schematic. Also, the required interpretation of the simulation results is given.

Additionally, Appendix A contains a list of known (non-trivial) errors as of April 2016 in 'CMOS Integrated Circuit Simulation with LTspice IV – a Tutorial Guide' (1<sup>st</sup> edition, 2015).

Often, there is not just one possible way of solving the problems. Several options exist when drawing a schematic in LTspice and several different simulations may be specified in order to arrive at a solution, so the solutions given here should just be taken as examples of how the simulations may be performed.

The problems are reprinted from 'CMOS Integrated Circuit Simulation with LTspice IV – a Tutorial Guide', and page and figure references given in the problems are to pages and figures from this book. However, for convenience, several of the figures referred to in the problems are also shown here. When the problems refer to the BSIM transistor models from fig. 3.10 on page 77, fig. 6.2 on page 184 (or fig. P3.2 on page 98 and fig. P3.3 on page 99), you may turn to the Introduction in the present book to find out how to create the model file.

The simulations in this book have been performed using LTspice version 4.23j, dated 29 February 2016.

I hope you find the problems and solutions useful. If you find typos or errors, I would appreciate your feedback. Suggestions for improvement are also welcome. You may send them to me by email, eb@elektro.dtu.dk.

### Erik Bruun

Department of Electrical Engineering, Technical University of Denmark.

### Introduction

The file 'BSIM3\_035.lib' is used in several of the problems in this book. It is derived from the file 'p35\_model\_card.inc' contained in the zip archive 'p35.zip' which can be downloaded from (Chan Carusone, Johns & Martin 2014). A few of the parameters in 'p35\_model\_card.inc' are deleted since they are ignored by LTspice anyway, and the parameters VTHO, TOX, UO, CJ, CJSW in 'p35\_model\_card.inc' which depend on process corners are given their nominal values for a typical process. The parameters which are deleted will not influence the simulation results significantly for normal values of transistor geometries. Also, the transistor models are named 'NMOS-BSIM' and 'PMOS-BSIM' rather than just 'NMOS' and 'PMOS' in order to emphasize that they are BSIM models, not just the default Spice models.

The following page shows the file 'p35\_model\_card.inc' with the modifications introduced for the model file 'BSIM3\_035.lib' used in this book.

```

*p35 model cardBSIM 035.lib

.MODEL NMOS-BSIM NMOS

LEVEL = 49

+DVTOW = 0 DVT1W = 0 DVT2W = 0

+DVTO = 2.87E+00 DVT1 = 5.86E-01 DVT2 = -1.26E-01

+U0 = \(^{1}\)360\(^{\text{*proc delta**proc delta*}}\) UA = -8.48E-10 UB = 2.27E-18

+UC = 3.27E-11 VSAT = 1.87E+05 A0 = 1.22E+00

+AGS = 2.06E-01 B0 = 9.60E-07 B1 = 4.95E-06

+KETA = -1.67E-04 A1 = 0 A2 = 3.49E-01

+RDSW = 8.18E+02 PRWG = 2.35E-02 PRWB = -8.12E-02

+WR = 9.98E-01 WINT = 1.55E-07 DWG = -4.27E-09

+RDSW = 8.18E+02 PRWG = 2.35E-02 PRWB = -8.12E-02

+WR = 9.98E-01 WINT = 1.55E-07 LINT = 4.51E-10

+XL = -5.00E-08 XW = 1.50E-07 — DWG = -4.27E-09

+DWB = 4.07E-09 VOFF = -4.14E-02 NFACTOR = 1.61E+00

+CIT = 0 CDSC = 2.39E-04 CDSCD = 0.00E+00

+CDSCB = 0 ETAO = 1 ETAB = -1.99E-01

+DSUB = 1 PCLM = 1.32E+00 PDIBLC1 = 2.42E-04

+PDIBLC2 = 8.27E-03 PDIBLCB = -9.99E-04 DROUT = 9.72E-04

+PSCBE1 = 7.24E+08 PSCBE2 = 9.96E-04 PVAG = 1.00E-02

+DELTA = 1.01E-02 RSH = 3.33E+00 MOBMOD = 1

+PRT = 0 UTE = -1.5 KT1 = -1.11E-01

+KT1L = 0 KT2 = 2.22E-02 UA1 = 4.34E-09

+UB1 = -7.56E-18 UC1 = -5.62E-11 AT = 3.31E+04

+WL = 0 WLN = 9.95E-01 WW = 0

+WWN = 1.00E+00 WWL = 0 LL = 0

+LLN = 1 LW = 0 LWN = 1

+LUL = 0 CAPMOD = 2 XPART = 0.5

+CGDO = 2.76E-10 CGSO = 2.76E-10 CGBO = 1.00E-12

+CJSW = -1.28E-10/Proc_delta' PBS = 7.95E-01 MJ = 3.53E-01

+CJSWG = 1.81E-10 PBSWG = 7.96E-01 MJSWG = 1.74E-01

+CF = 0 PVTHO = -1.80E-02 PRDSW = -7.56E+01

+PK2 = 4.48E-05 WKETA = -1.33E-03 LKETA = -8.91E-03

+WL = 1 WINT = 1.47E-07 DWG = -1.09E-08

+XL = -4.98E-08 XW = 1.51E-07 DWG = -1.09E-08

+DWB = 1.14E-08 VOFF = -1.29E-01 NFACTOR = 2.01E+00

+CTT = 0 CDSC = 2.40E-04 CDSCD = 0

+CDSCB = 0 ETAO = 4.07E-02 ETAB = 6.84E-03

+DSUB = 3.21E-01 PCLM = 5.96E+00 PDIBLC1 = 2.89E-03

+PDIBLC2 = -1.45E-06 PDIBLCB = -1E-03 DROUT = 9.93E-04

+PSCBE1 = 7.88E+10 PSCBE2 = 5E-10 PVAG = 15

+DELTA = 9.96E-03 RSH = 2.6 MOBMOD = 1

+PRT = 0 UTE = -1.5 KT1 = -1.09E-01

+KT1L = 0 KT2 = 2.19E-02 UA1 = 4.34E-09

+UB1 = -7.62E-18 UC1 = -5.63E-11 AT = 3.28E+04

+WL = 0 WLN = 1 WW = 0

+WWN = 1.00E+00 WWL = 0 LL = 0

+LUN = 1 LW = 0 LWN = 1

+LWL = 0 CAPMOD = 2.01E+00 XPART = 0.5

+CGDO = 2.10E-10 CGSO = 2.12E-10 CGBO = 1.00E-12

+CJSW = -3.2e-10/proc_delta' PB = 9.83E-01 MJ = 5.79E-01

+CJSWG = 4.41E-11 PBSWG = 9.85E-01 MJSWG = 3.58E-01

+CF = 0 PVTHO = 2.58E-02 PRDSW = -3.98E+01

+PK2 = 2.02E-03 WKETA = 2.72E-03 LKETA = -7.14E-03

```

For several of the problems for tutorial 6, the file 'BSIM3\_O35PVT.lib' is used. This file is derived from the file 'BSIM3\_O35.lib' by introducing the speed parameters 'SN' and 'SP' for the process dependent parameters VTHO, TOX, UO, CJ, CJSW. The nominal values for typical process parameters are replaced by the expressions given below.

### NMOS transistors:

$$\begin{array}{lll} \text{VTHO} &=& \left\{0.48-\text{SN}/\text{10}\right\} \\ \text{TOX} &=& \left\{7.8\text{E}-9/(1+\text{SN}/\text{20})\right\} \\ \text{UO} &=& \left\{360*(1+\text{SN}/\text{20})**2\right\} \\ \text{CJ} &=& \left\{9\text{e}-4/(1+\text{SN}/\text{20})\right\} \\ \text{CJSW} &=& \left\{2.8\text{e}-10/(1+\text{SN}/\text{20})\right\} \end{array}$$

### PMOS transistors:

$$\begin{array}{lll} \text{VTHO} &=& \{-0.6 + \text{SP}/10\} \\ &\text{TOX} &=& \{7.8\text{E} - 9/(1 + \text{SP}/20)\} \\ &\text{UO} &=& \{150*(1 + \text{SP}/20)**2\} \\ &\text{CJ} &=& \{14\text{e} - 4/(1 + \text{SP}/20)\} \\ &\text{CJSW} &=& \{3.2\text{e} - 10/(1 + \text{SP}/20)\} \end{array}$$

### References

Chan Carusone, T., Johns, D. & Martin, K. 2014, *Analog Integrated Circuit Design, Netlist and model files*. Retrieved from http://analogicdesign.com/students/netlists-models/

### Tutorial 1 – Resistive Circuits

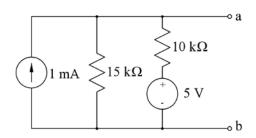

1.1

Figure P1.1

For the circuit shown in fig. P1.1, find the Thévenin voltage  $V_t$  and the Thévenin resistance  $R_t$ . A load resistor of  $R_L = 3 \text{ k}\Omega$  is now connected between the terminals a and b. Find the power dissipated in  $R_L$ .

### **Solution:**

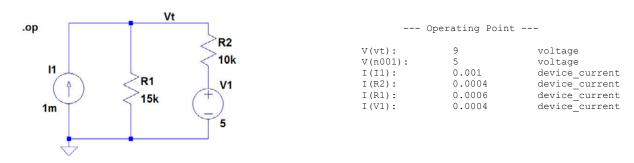

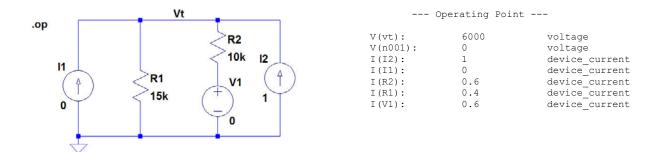

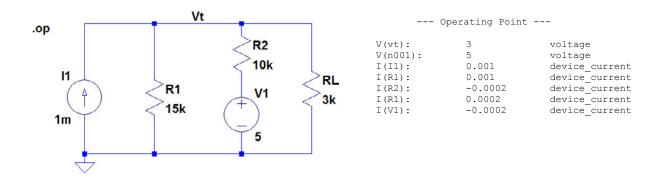

For finding the Thévenin voltage  $V_t$ , we run the '.op' simulation shown below. From the simulation output, we find  $V_t = V(vt) = 9 \text{ V}$ .

For finding the Thévenin resistance  $R_t$ , we reset the voltage source and the current source and apply a current source of 1 A between terminal a and b and find the voltage between a and b as shown below. From the simulation output, we find  $R_t = V(vt)/1$  A = 6 k $\Omega$ .

For finding the power dissipated in a load resistor of  $R_L = 3 \text{ k}\Omega$  connected between the terminals a and b, we run the '.op' simulation shown below.

From the simulation output, we find  $P = V(vt)I(R1) = 3 \text{ V} \times 0.001 \text{ A} = 3 \text{ mW}$ . By moving the cursor over RL after the simulation, the dissipation can also be read directly in the status bar at the bottom of the LTspice program window.

Figure P1.2

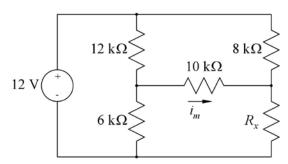

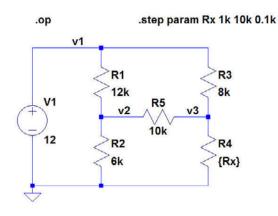

For the circuit shown in fig. P1.2, determine the value of resistor  $R_x$  so that the current  $i_m$  in the 10 k $\Omega$  resistor is 30  $\mu$ A.

### **Solution:**

For this circuit, we run a simulation where  $R_x$  is varied over a suitable range, and we plot  $i_m$  versus  $R_x$ . In the schematic below,  $i_m = -\mathbb{I}(\mathbb{R}5)$  because  $\mathbb{R}5$  is inserted with just one rotation of the resistor symbol, causing the positive direction of current flow in  $\mathbb{R}5$  to be from right to left. From the simulation plot, we find that  $R_x = 3.31 \text{ k}\Omega$  results in  $i_m = 30 \text{ \mu}\text{A}$ .

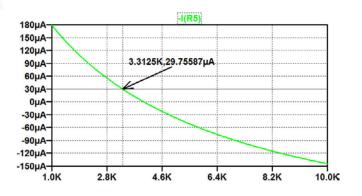

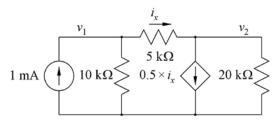

Figure P1.3

For the circuit shown in fig. P1.3, determine the value of the voltages  $v_1$  and  $v_2$  and the current  $i_x$ .

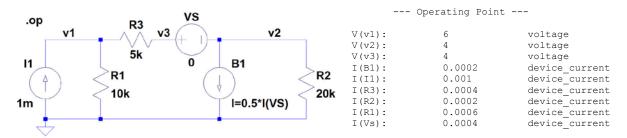

### **Solution:**

For this circuit, we need a current controlled current source. This can be achieved using the arbitrary controlled current source as shown below. The voltage source VS is inserted because the controlling current must be the current through a voltage source. The current  $i_x$  is the current through VS.

From the output file, we find  $v_1 = 6 \text{ V}$ ,  $v_2 = 4 \text{ V}$  and  $i_x = I(Vs) = 0.4 \text{ mA}$ .

1.4  $\begin{array}{c|c}

& 10 \text{ k}\Omega \\

\hline

& 5 \text{ k}\Omega \\

\hline

& i_x \\

\hline

& 5 \text{ k}\Omega

\end{array}$   $\begin{array}{c|c}

& 0.5 \text{ V/mA} \times i_x \\

\hline

& 0.5 \text{ V/$

Figure P1.4

For the circuit shown in fig. P1.4, find the equivalent resistance looking into terminals a - b.

### **Solution:**

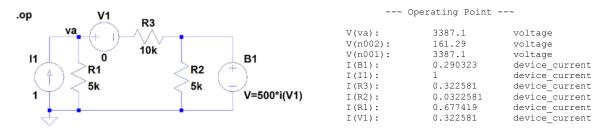

For this circuit, we need a current controlled voltage source. This can be achieved using the arbitrary controlled voltage source as shown below. The voltage source V1 is inserted because the controlling current must be the current through a voltage source. Additionally, a current source of 1 A is connected between terminals a and b, and the equivalent resistance is found as the voltage between a and b divided by 1 A. From the output file, we find  $R_{ab} = V(va)/1$  A = 3.387 k $\Omega$ .

Discover the truth at www.deloitte.ca/careers

Figure P1.5

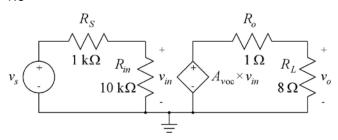

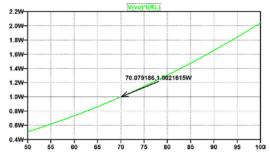

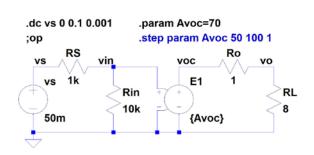

For the circuit shown in fig. P1.5, find the value of the gain  $A_{voc}$  which gives an output power in  $R_L$  of 1 W when the signal voltage  $v_s$  is 50 mV. With this value of  $A_{voc}$ , plot the output power versus the input voltage for  $v_s$  in the range from 0 mV to 100 mV.

### **Solution:**

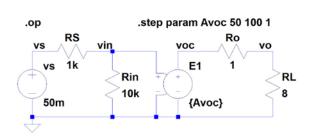

For this circuit, we define  $A_{voc}$  as a parameter and step it over a suitable range when running a '.op' simulation. From a plot of V(vo)\*I(RL), we find that  $A_{voc} = 70 \text{ V/V}$  results in a power of 1 W in  $R_L$ , see simulation below.

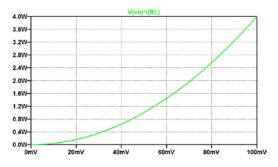

For simulating the output power versus the input voltage, we run a '.dc' simulation with the parameter Avoc set to 70, see simulation below, showing the output power versus  $v_s$ .

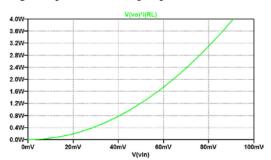

For showing the output power versus  $v_{in}$ , we move the cursor in the plot window to the x-axis and apply a left click on the mouse. This opens a specification window for the x-axis as shown below where we can change the 'Quantity Plotted' from Vs to V(vin), resulting in a plot of the output power versus  $v_{in}$ .

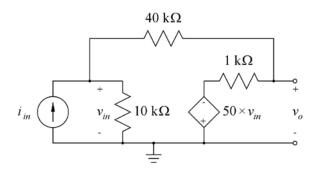

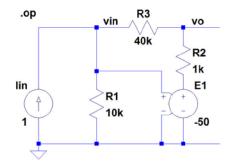

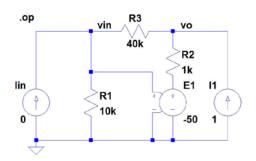

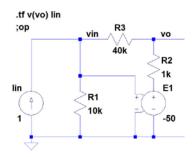

Figure P1.6

The circuit shown in fig. P1.6 is a transresistance amplifier built from an inverting voltage amplifier with an input resistance of 10 k $\Omega$ , an output resistance of 1 k $\Omega$  and an open circuit voltage gain of -50 V/V and a feedback resistor with a value of 40 k $\Omega$ . Find the open circuit transresistance  $R_{moc}$ , the input resistance  $R_{in}$  and the output resistance  $R_o$  of the resulting transresistance amplifier.

### **Solution:**

For finding the open circuit transresistance  $R_{moc}$  and the input resistance  $R_{in}$ , we run a '.op' simulation with an input current signal source of 1 A, see below. The input resistance is found as  $v_{in}/i_{in} = V(vin)/1$  A, and the transresistance is found as  $v_o/i_{in} = V(vo)/1$  A.

From the output file, we find  $R_{moc} = V(vo)/1 \text{ A} = -36.28 \text{ k}\Omega$  and  $R_{in} = V(vin)/1 \text{ A} = 744 \Omega$ .

|                    | Operating Point |                |

|--------------------|-----------------|----------------|

|                    |                 |                |

| V(vin):            | 744.102         | voltage        |

| V(vo):             | -36279.5        | voltage        |

| V(n001):           | -37205.1        | voltage        |

| <pre>I(Iin):</pre> | 1               | device current |

| I(R2):             | 0.92559         | device current |

| I(R3):             | -0.92559        | device current |

| I(R1):             | 0.0744102       | device current |

| I(E1):             | 0.92559         | device current |

For finding the output resistance  $R_o$ , we run a '.op' simulation with a current source of 1 A connected to the output and with the input current source reset. The output resistance is found as V(v0)/1 A. From the output file, we find  $R_o = V(v0)/1$  A = 90.7  $\Omega$ .

|                                                                                  | operating roint                                                    |                                                                                     |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| V(vin):<br>V(vo):<br>V(n001):<br>I(I1):<br>I(Iin):<br>I(R2):<br>I(R3):<br>I(R1): | 18.1488<br>90.7441<br>-907.441<br>1<br>0<br>0.998185<br>0.00181488 | voltage voltage voltage device_current device_current device_current device_current |

| I(E1):                                                                           | 0.998185                                                           | device_current                                                                      |

An alternative simulation giving both input resistance, output resistance and transresistance in just one simulation is the '.tf' simulation shown below.

| Transfer                                                           | Function |                                    |

|--------------------------------------------------------------------|----------|------------------------------------|

| Transfer_function:<br>iin#Input_impedance:<br>output_impedance_at_ |          | transfer<br>impedance<br>impedance |

Figure P1.7

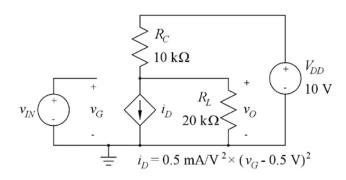

Fig. P1.7 shows a nonlinear transconductance amplifier. Find the values of bias voltages and currents for an input bias voltage (quiescent voltage) of  $V_{IN} = 1.0$  V. Plot the output voltage  $v_O$  for the input voltage in the range from 0.5 V to 1.8 V. Find the small-signal voltage gain  $v_O/v_{in}$  for an input bias voltage of  $V_{IN} = 1.0$  V and plot the small-signal voltage gain as a function of the input bias voltage for the input bias voltage in the range from 0.5 V to 1.8 V.

### **Solution:**

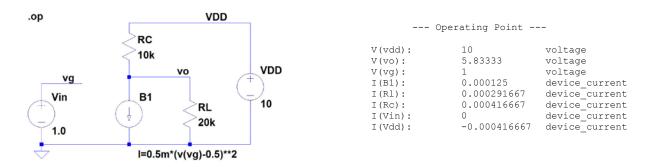

For finding the bias voltages and currents, we run a '.op' simulation as shown below. From the output file, we find  $I_D = I(B1) = 0.125$  mA,  $I_C = I(Rc) = 0.417$  mA,  $I_L = I(R1) = 0.292$  mA and  $V_O = V(vo) = 5.83$  V.

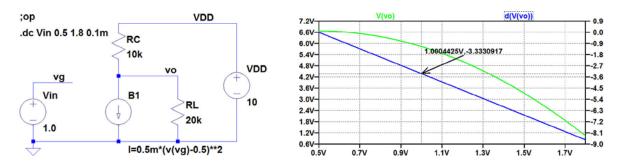

For plotting the output voltage and the small-signal voltage gain versus input bias voltage, we run a '.dc' simulation as shown below. The voltage gain is shown as the derivative of the output voltage, d(V(vo)).

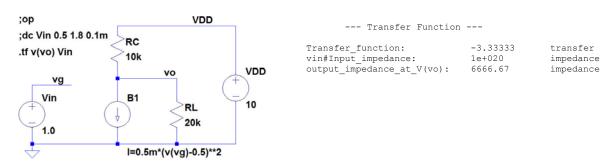

The small-signal gain for  $V_{IN} = 1.0 \text{ V}$  may be found from the plot above, or it may be found from a '.tf' simulation as shown below. From this, we find a small-signal gain of -3.33 V/V.

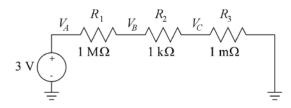

Figure P1.8

- Fig. P1.8 shows a series connection of three resistors and a voltage source.

- Try three different ways of drawing the schematic:

- (1): Insert the components and draw the connections between them.

- (2): Insert the components (including the ground symbols) and draw an unbroken wire (hotkey 'F3') from leftmost ground symbol across the components to rightmost ground symbol.

- (3): Insert the ground symbols, draw an unbroken wire between them, and then insert the component directly on top of the wire.

Observe how LTspice 'cleans up' the wiring.

voltage

voltage

Find the voltages  $V_A$ ,  $V_B$  and  $V_C$ .

### **Solution:**

(1) The figure below shows the resulting schematic and the output file for a '.op' simulation. From the output file, we find  $V_A = 3.0000 \text{ V}$ ,  $V_B = 2.997 \text{ mV}$  and  $V_C = 2.997 \text{ nV}$ .

(2) When inserting the components and drawing a wire across the components, the wire appears across the components during the insertion process as shown in the figure below, but when the insertion is completed, the wiring is cleaned up, resulting in the schematic shown above.

(3) When inserting an unbroken wire first and the components afterwards on top of the wire, the cleaning up takes place when completing the insertion. The figure below shows the schematic when the voltage source insertion has been completed and the resistor insertion is in progress.

### Tutorial 2 - Circuits with Capacitors and Inductors

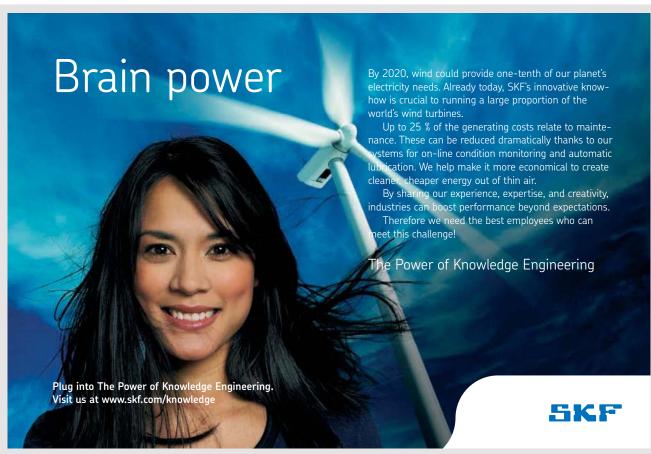

Figure P2.1

For the circuit shown in fig. P2.1, assume that the switch is closed at time t = 0 and re-opened at time t = 100 ms. Find the value of the voltage  $v_{R_2}$  immediately after the switch is closed. Find the value of  $v_{R_2}$  immediately before the switch is re-opened. Find the value of  $v_{R_2}$  immediately after the switch is re-opened. Plot  $v_{R_2}$  versus time for  $0 \le t \le 200$  ms. Plot the capacitor voltage versus time and find the time constants for the charging and discharging of the capacitor C.

### **Solution:**

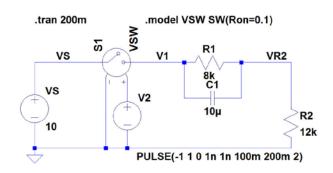

The figure below shows the circuit with a voltage controlled switch, controlled by a voltage V2 specified as a time varying voltage. For the specification, we use a 'PULSE' waveform with rise time and fall time of 1 ns which is much shorter than the pulse width of 100 ms. For the voltage controlled switch, a '.model' specification has been inserted, changing the on-resistance from the default value of 1  $\Omega$  to a value of 0.1  $\Omega$ . From the figure, we find the value of  $v_{R_2}$  immediately after the switch is closed to be 10 V, and we find the value of  $v_{R_2}$  immediately before the switch is re-opened to be 6.5 V. The value of  $v_{R_2}$  immediately after the switch is re-opened to be 0 V.

The time constants for charging and discharging of the capacitor may be evaluated from the previous simulation but an easier, alternative approach is to run transient simulations with only dc voltage sources and a specification of initial voltages for the capacitor.

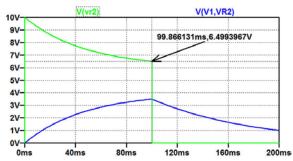

The figure below shows a simulation for finding the charging time constant. As the limiting value of  $v_{R_2}$  for  $t \to \infty$  is  $V_S R_1/(R_1+R_2)$ , it is convenient to select  $V_S = (1+R_2/R_1)/(1-e^{-1}) = 3.955$  V, implying that a capacitor voltage of 1 V is reached for  $t = \tau$ . Also, the initial value of the capacitor voltage must be specified to 0 V. From the figure, we find  $\tau = 48$  ms.

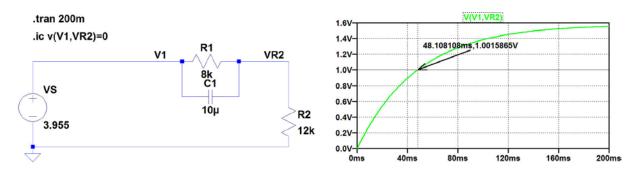

For finding the time constant for discharging with the switch open, we disconnect  $V_S$  and specify the initial value of the capacitor voltage to be e = 2.718 V so that the capacitor voltage reaches a value of 1 V after  $t = \tau$ , see figure below. From this simulation, we find  $\tau = 80$  ms.

Figure P2.2

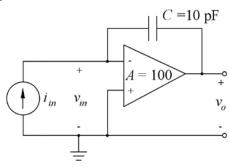

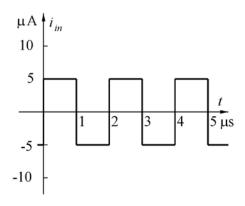

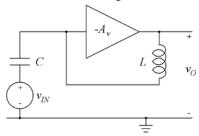

For the circuit shown in fig. P2.2, plot the output voltage  $v_o$  versus time t for  $0 \le t \le 5$  µs. You may assume that the amplifier has infinite input resistance and zero output resistance. Also, assume that the initial value of the input and output voltage at t = 0 is 0 V. Which initial value of the input voltage  $v_{in}$  will result in a mean value of 0 V for the output voltage  $v_o$ ?

### **Solution:**

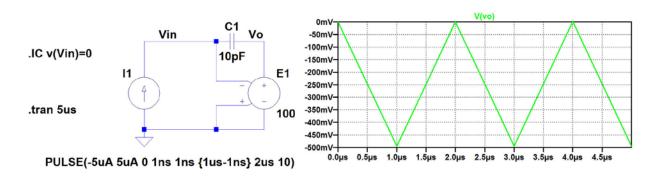

The figure below shows the circuit with the amplifier modelled by a voltage controlled voltage source. The time varying input current is specified by a 'PULSE' waveform with rise time and fall time of 1 ns which is much shorter than the pulse width of 1  $\mu$ s, and with the specification shown below, the mean input current is 0. The initial value of the input voltage is set by the '.IC' directive.

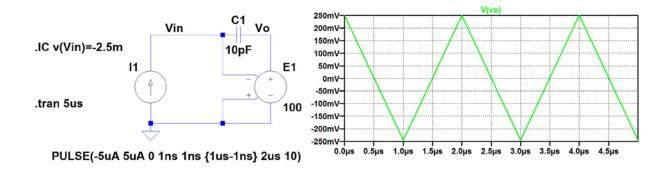

From the plot of the resulting output waveform, we find a mean value of  $-250 \,\text{mV}$  for the output voltage, so in order to obtain a mean value of 0 V for the output voltage, the initial value of the input voltage must be changed by  $-2.5 \,\text{mV}$  since the gain of the inverting voltage controlled voltage source is 100. Thus, the required initial value of  $v_{in}$  is  $-2.5 \,\text{mV}$  as confirmed by the simulation shown below.

# With us you can shape the future. Every single day.

For more information go to: www.eon-career.com

Your energy shapes the future.

e.on

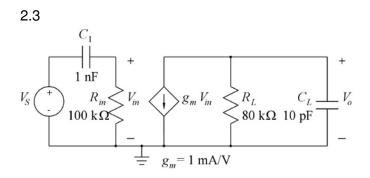

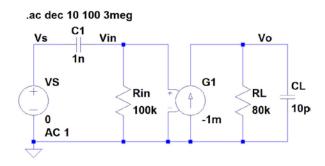

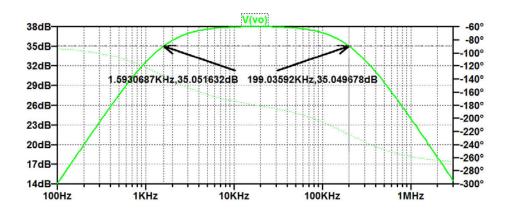

Figure P2.3

For the circuit shown in fig. P2.3, find the midband gain, the upper and lower half-power (-3 dB) frequencies and the 3-dB bandwidth. Plot the output voltage  $V_o$  versus frequency in a Bode plot covering a frequency range which extends from approximately one decade below the lower half-power frequency to approximately one decade above the upper half-power frequency.

### **Solution:**

The figure below shows the circuit and the simulated Bode plot from 100 Hz to 3 MHz. From the Bode plot, we find a midband gain of 38 dB, a lower -3 dB frequency of 1.59 kHz and an upper -3 dB frequency of 199 kHz. The 3-dB bandwidth is 199 kHz -1.59 kHz = 197.41 kHz.

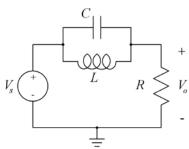

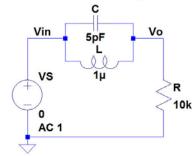

Figure P2.4

For the notch filter shown in fig. P2.4, plot  $V_o$  versus frequency in a frequency range showing the notch and the 3-dB bandwidth. Assume  $L=1~\mu\text{H}$ , C=5~pF and  $R=10~\text{k}\Omega$ . From the plot, find the notch frequency, the bandwidth and the quality factor Q.

### **Solution:**

The figure below shows the circuit and the simulated Bode plot from 69 MHz Hz to 73 MHz. Notice that a large number of points per octave has been specified (10000) in order to show the notch. In order to find the frequency range to plot, it may be a good idea to calculate the resonance frequency from  $f_{res} = (2\pi\sqrt{LC})^{-1} = 71.18$  MHz. From the Bode plot, we find a notch frequency of 71.2 MHz, a 3-dB bandwidth of (72.79-69.61) MHz = 3.18 MHz and a quality factor Q = 71.2/3.18 = 22.4. Analytically, the quality factor is calculated from  $Q = R\sqrt{C/L} = 22.4$ .

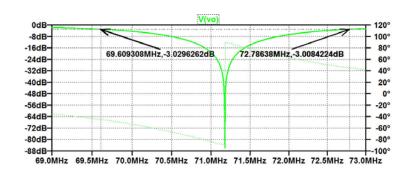

Figure P2.5

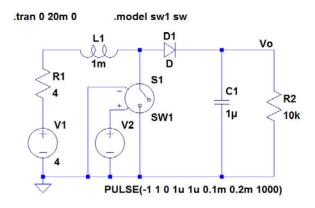

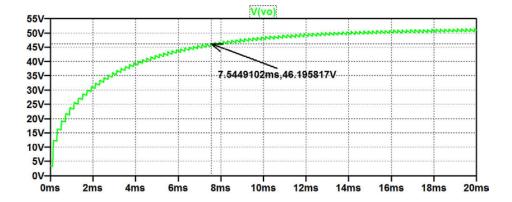

The circuit shown in fig. P2.5 is a dc-dc converter which converts a dc voltage of 4 V into a high voltage  $V_O$ . The switch is an electronic switch which opens and closes with a frequency of 5 kHz and a duty cycle of 50%, starting at time t=0. The diode can be assumed to be modeled by the default Shockley diode model. Initially, the current in the inductor is 0 and the output voltage  $V_O$  is 0. Find the dc output voltage for  $t \to \infty$  and find the time required for  $V_O$  to reach 90% of the final value.

### **Solution:**

The figure below shows the circuit with a voltage controlled switch controlled by a voltage V2 specified as a time varying voltage. For the specification, a 'PULSE' waveform with rise time and fall time much shorter than the pulse width is used. For the diode, no '.model' specification is needed for the default Shockley model. For the voltage controlled switch, a '.model' specification has been inserted using the default switch parameters. If you do not insert the '.model' specification, the simulation will still run with the default switch model but an error message will be produced.

The figure below shows the simulated output voltage from 0 to 20 ms. From the simulation, we find an output voltage of about 51 V for  $t \to \infty$  and a rise time of about 7.5 ms for reaching 90% of the final value.

### Tutorial 3 – MOS Transistors

3.1

$$W = 10$$

μm,  $L = 1$  μm  $K_p = 55$  μA/V<sup>2</sup>,  $V_{to} = -0.71$  V,  $\lambda = 0.16$  V<sup>-1</sup>,  $\gamma = 0.75$   $\sqrt{V}$ ,  $|2\Phi_F| = 0.7$  V.

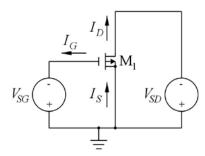

Figure P3.1

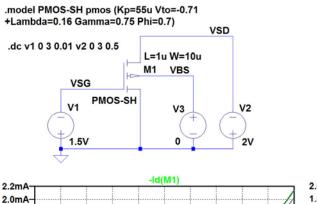

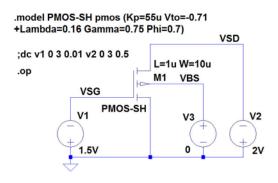

For the PMOS transistor shown in fig. P3.1, simulate and plot the input characteristics  $I_D$  versus  $V_{SG}$  and  $\partial i_D/\partial v_{SG}$  for  $V_{SD}=0$ , 0.5, 1.0, 1.5, 2.0, 2.5 and 3.0 V. Use the model parameters and transistor dimensions shown in the figure. Find the bias current  $I_D$  and the small-signal parameters  $g_m$ ,  $g_{mb}$  and  $g_{ds}$  for a bias point of  $V_{SG}=1.5$  V and  $V_{SD}=2.0$ V.

### **Solution:**

The figure below shows the schematic for simulating the input characteristics. Also shown are the resulting plots of  $I_D$  versus  $V_{SG}$  and  $\partial i_D/\partial v_{SG}$  (or  $g_m$ ) for  $V_{SD}=0$  V (green curves), 0.5 V (blue curves), 1.0 V (red curves), 1.5 V (cyan curves), 2.0 V (purple curves), 2.5 V (grey curves) and 3.0 V (dark green curves). You may notice that when the transistor is in the triode region ( $|V_{DS}| < |V_{GS}| - |V_t|$ ),  $g_m$  is independent of  $V_{SG}$ , see equation (3.11) in 'CMOS Integrated Circuit Simulation with LTspice IV – a Tutorial Guide'.

For finding the bias current and the small-signal parameters for a bias point of  $V_{SG} = 1.5 \text{ V}$  and  $V_{SD} = 2.0 \text{ V}$ , we run a '.op' simulation. The bias values and the small-signal parameters are given in the error log file ('Ctrl-L') from this simulation, see below where the requested parameters are underlined. Notice that in LTspice, the drain current is defined positive into the transistor, whereas in fig. P3.1, it is defined positive out of the transistor.

| Semicondu | ctor Device Operating Poin | its:    |

|-----------|----------------------------|---------|

|           | MOSFET Tran                | sistors |

| Name:     | m1                         |         |

| Model:    | pmos-sh                    |         |

| Id:       | -2.27e-04                  |         |

| Vgs:      | -1.50e+00                  |         |

| Vds:      | -2.00e+00                  |         |

| Vbs:      | 0.00e+00                   |         |

| Vth:      | -7.10e-01                  |         |

| Vdsat:    | -7.90e-01                  |         |

| Gm:       | 5.74e-04                   |         |

| Gds:      | 2.75e-05                   |         |

| Gmb ·     | 2 57e-04                   |         |

.MODEL NMOS-BSIM NMOS LEVEL = 49 +VERSION = 3.1 TNOM = 27 TOX = 7.8E-9 +XJ = 1E-07 NCH = 2.18E+17 VTH0 = 0.48 +K1 = 6.07E-01 K2 = 1.24E-03 K3 = 9.68E+01 +K3B = -9.84E+00 W0 = 2.02E-05 NLX = 1.62E-07 +DVT0W = 0 DVT1W = 0 DVT2W = 0 +DVT0 = 2.87E+00 DVT1 = 5.86E-01 DVT2 = -1.26E-01 +U0 = 360 UA = -8.48E-10 UB = 2.27E-18 +UC = 3.27E-11 VSAT = 1.87E+05 A0 = 1.22E+00 +AGS = 2.06E-01 B0 = 9.60E-07 B1 = 4.95E-06 +KETA = -1 67F-04 A1 = 0 A2 = 3 49F-01 +RDSW = 8.18E+02 PRWG = 2.35E-02 PRWB = -8.12E-02 +WR = 9.98E-01 WINT = 1.55E-07 LINT = 4.51E-10 +DWG = -4 27F-09 +DWB = 4.07E-09 VOFF = -4.14E-02 NFACTOR = 1.61E+00 +CIT = 0 CDSC = 2.39E-04 CDSCD = 0.00E+00 +CDSCB = 0 ETA0 = 1 ETAB = -1.99E-01 +DSUB = 1 PCLM = 1.32E+00 PDIBLC1 = 2.42E-04 +PDIBLC2 = 8.27E-03 PDIBLCB = -9.99E-04 DROUT = 9.72E-04 +PSCBE1 = 7.24E+08 PSCBE2 = 9.96E-04 PVAG = 1.00E-02 +DELTA = 1.01E-02 RSH = 3.33E+00 MOBMOD = 1 +PRT = 0 UTE = -1.5 KT1 = -1.11E-01 +KT1L = 0 KT2 = 2.22E-02 UA1 = 4.34E-09 +UB1 = -7.56E-18 UC1 = -5.62E-11 AT = 3.31E+04 +WL = 0 WLN = 9.95E-01 WW = 0 +WWN = 1.00E+00 WWL = 0 LL = 0 +LLN = 1 LW = 0 LWN = 1 +LWL = 0 CAPMOD = 2 XPART = 0.5 +CGDO = 2.76E-10 CGSO = 2.76E-10 CGBO = 1.00E-12 +CJ = 9e-4 PB = 7.95E-01 MJ = 3.53E-01 +CJSW = 2.8e-10 PBSW = 7.98E-01 MJSW = 1.73E-01 +CJSWG = 1.81E-10 PBSWG = 7.96E-01 MJSWG = 1.74E-01 +CF = 0 PVTH0 = -1.80E-02 PRDSW = -7.56E+01 +PK2 = 4.48E-05 WKETA = -1.33E-03 LKETA = -8.91E-03

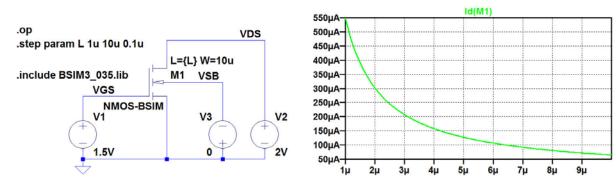

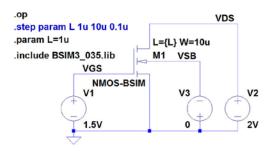

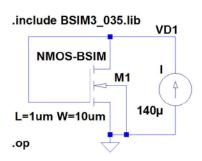

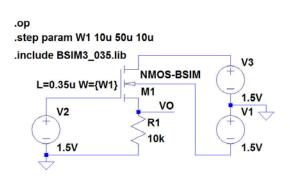

For an NMOS transistor with the transistor model shown in fig. P3.2 (BSIM3 0.35  $\mu$ m model, fig. 3.10) and channel width  $W=10~\mu$ m, simulate and plot  $I_D$  versus the channel length L in the interval 1  $\mu$ m  $< L < 10~\mu$ m for a bias point of  $V_{GS}=1.5~\rm V$ ,  $V_{DS}=2.0~\rm V$  and  $V_{SB}=0~\rm V$ . Find the bias current  $I_D$  and the small-signal parameters  $g_m$ ,  $g_{mb}$  and  $g_{ds}$  for  $L=1~\mu$ m and for  $L=5~\mu$ m in the bias point.

Hint: Define L as a parameter, compare page 26.

Figure P3.2

### **Solution:**

The figure below shows the schematic for simulating the drain current. The channel length L is defined as a parameter which is stepped from 1  $\mu m$  to 10  $\mu m$ . The transistor model is included in a separate model file, 'BSIM3\_035.1ib'. The drain current is found from a '.op' simulation.

For finding the bias current  $I_D$  and the small-signal parameters  $g_m$ ,  $g_{mb}$  and  $g_{ds}$  for L=1  $\mu m$  and for L=5  $\mu m$  in the bias point of  $V_{GS}=1.5$  V,  $V_{DS}=2.0$  V and  $V_{SB}=0$  V, we specify the value of L using a 'param' directive with the 'step param' directive changed into a comment, see the figure on the following page with L=1  $\mu m$ .

The bias point information is given in the error log file from a '.op' simulation. The error log files for  $L=1~\mu m$  and  $L=5~\mu m$  are shown below with an underlining of the requested parameters. We notice that with the BSIM transistor model, neither the bias current, nor the transconductances  $(g_m \text{ and } g_{mb})$  scale by a factor of 5 as predicted by the Shichman-Hodges model.

L=1e-6:

| Name:  | m1        |  |

|--------|-----------|--|

| Model: | nmos-bsim |  |

| Id:    | 5.48e-04  |  |

| Vgs:   | 1.50e+00  |  |

| Vds:   | 2.00e+00  |  |

| Vbs:   | 0.00e+00  |  |

| Vth:   | 5.43e-01  |  |

| Vdsat: | 6.21e-01  |  |

| Gm:    | 9.92e-04  |  |

| Gds:   | 1.03e-05  |  |

| Gmb    | 2.63e-04  |  |

L=5e-6:

Semiconductor Device Operating Points:

--- BSIM3 MOSFETS ---

| Name:  | m1        |

|--------|-----------|

| Model: | nmos-bsim |

| Id:    | 1.27e-04  |

| Vgs:   | 1.50e+00  |

| Vds:   | 2.00e+00  |

| Vbs:   | 0.00e+00  |

| Vth:   | 5.10e-01  |

| Vdsat: | 7.45e-01  |

| Gm:    | 2.45e-04  |

| Gds:   | 1.94e-06  |

| Gmb    | 6.53e-05  |

|        |           |

.MODEL PMOS-BSIM PMOS LEVEL = 49 +VERSION = 3.1 TNOM = 2.69E+01 TOX = 7.8E-9 +XJ = 1.00E-07 NCH = 8.44E+16 VTH0 = -0.6 +K1 = 4.82E-01 K2 = -2.13E-02 K3 = 8.27E+01 +K3B = -5 W0 = 5.24E-06 NLX = 2.49E-07 +DVT0W = 0.00E+00 DVT1W = 0 DVT2W = 0 +DVT0 = 3.54E-01 DVT1 = 7.52E-01 DVT2 = -2.98E-01 +U0 = 150 UA = 1E-10 UB = 1.75E-18 +UC = -2.27E-11 VSAT = 2.01E+05 A0 = 1.04E+00 +AGS = 2.90E-01 B0 = 1.94E-06 B1 = 5.01E-06 +KETA = -3.85E-03.A1 = 4.20E-03.A2 = 1.00E+00 +RDSW = 4000 PRWG = -9.54E-02 PRWB = -1.92E-03 +WR = 1 WINT = 1.47E-07 LINT = 1.04E-10 +DWG = -1 09F-08 +DWB = 1.14E-08 VOFF = -1.29E-01 NFACTOR = 2.01E+00 +CIT = 0 CDSC = 2.40E-04 CDSCD = 0 +CDSCB = 0 ETA0 = 4.07E-02 ETAB = 6.84E-03 +DSUB = 3.21E-01 PCLM = 5.96E+00 PDIBLC1 = 2.89E-03 +PDIBLC2 = -1.45E-06 PDIBLCB = -1E-03 DROUT = 9.93E-04 +PSCBE1 = 7.88E+10 PSCBE2 = 5E-10 PVAG = 15 +DELTA = 9.96E-03 RSH = 2.6 MOBMOD = 1 +PRT = 0 UTE = -1.5 KT1 = -1.09E-01 +KT1L = 0 KT2 = 2.19E-02 UA1 = 4.34E-09 +UB1 = -7.62E-18 UC1 = -5.63E-11 AT = 3.28E+04 +WL = 0 WLN = 1 WW = 0 +WWN = 1.00E+00 WWL = 0 LL = 0 +LLN = 1 LW = 0 LWN = 1 +LWL = 0 CAPMOD = 2.01E+00 XPART = 0.5 +CGDO = 2.10E-10 CGSO = 2.12E-10 CGBO = 1.00E-12 +CJ = 14e-4 PB = 9.83E-01 MJ = 5.79E-01 +CJSW = 3.2e-10 PBSW = 9.92E-01 MJSW = 3.60E-01 +CJSWG = 4.41E-11 PBSWG = 9.85E-01 MJSWG = 3.58E-01 +CF = 0 PVTH0 = 2.58E-02 PRDSW = -3.98E+01 +PK2 = 2.02E-03 WKETA = 2.72E-03 LKETA = -7.14E-03

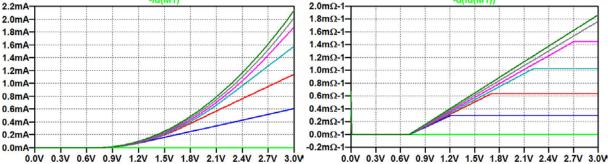

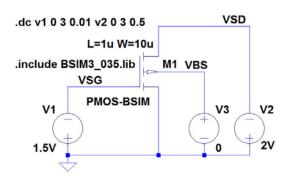

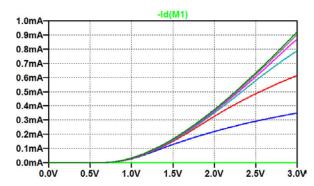

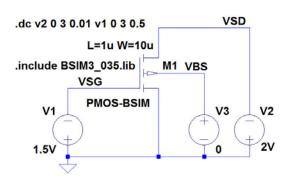

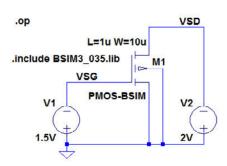

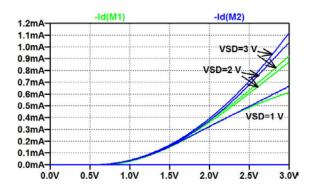

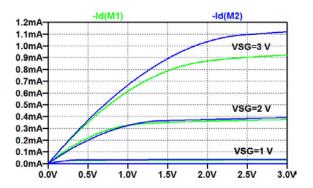

For a PMOS transistor with the transistor model shown in fig. P3.3 (BSIM3 0.35 µm model, fig. 3.10) and channel width W=10 µm and channel length L=1 µm, simulate and plot the input characteristics  $I_D$  versus  $V_{SG}$  for  $V_{SD}=0$ , 0.5, 1.0, 1.5, 2.0, 2.5 and 3.0 V. Assume  $V_{BS}=0$  V. Also simulate and plot the output characteristics  $I_D$  versus  $V_{SD}$  for  $V_{SG}=0$ , 0.5, 1.0, 1.5, 2.0, 2.5 and 3.0 V. Use the cursors to find  $I_D$  and  $\partial i_D/\partial v_{SD}$  for  $V_{SG}=1.5$  V,  $V_{BS}=0$  V and  $V_{SD}=2.0$  V.

Figure P3.3

### **Solution:**

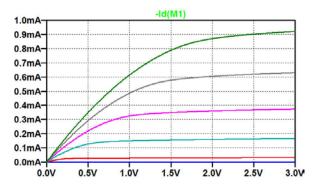

The figure below shows the schematic for simulating the input characteristics. Also shown is the resulting plot of  $I_D$  versus  $V_{SG}$  for  $V_{SD} = 0$  V (green curve), 0.5 V (blue curve), 1.0 V (red curve), 1.5 V (cyan curve), 2.0 V (purple curve), 2.5 V (grey curve) and 3.0 V (dark green curve). Because of the difference in sign conventions between textbooks and LTspice, the plot below shows -Id(M1) which is equal to  $I_D$  using the normal textbook convention.

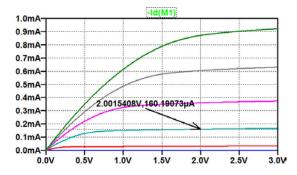

The figure below shows the schematic for simulating the output characteristics. Also shown is the resulting plot of  $I_D$  versus  $V_{SD}$  for  $V_{SG} = 0$  V (green curve, not visible because of the blue curve), 0.5 V (blue curve), 1.0 V (red curve), 1.5 V (cyan curve), 2.0 V (purple curve), 2.5 V (grey curve) and 3.0 V (dark green curve).

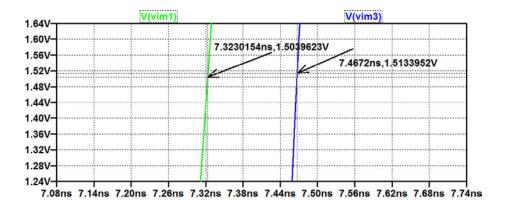

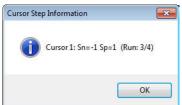

For finding  $I_D$  for  $V_{SG} = 1.5$  V,  $V_{BS} = 0$  V and  $V_{SD} = 2.0$  V, the output characteristics above are used with a cursor placed on the cyan curve, see figure below. The cursor is shifted from one curve to another by the up/down arrow keys. We find  $I_D = 0.16$  mA.

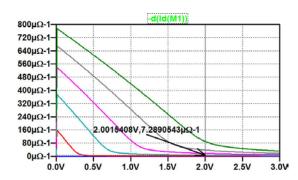

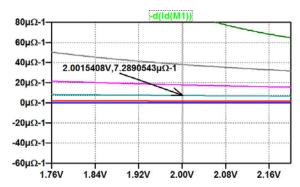

For finding  $\partial i_D/\partial v_{SD}$  for  $V_{SG}=1.5$  V,  $V_{BS}=0$  V and  $V_{SD}=2.0$  V, the derivative of  $I_D$  is plotted as shown below. It may be a good idea to zoom in on the relevant part of the characteristics as also shown in the figure. We find  $\partial i_D/\partial v_{SD}=7.3$   $\mu$ A/V.

.MODEL PMOS-BSIM PMOS LEVEL = 49 +VERSION = 3.1 TNOM = 2.69E+01 TOX = 7.8E-9 +XJ = 1.00E-07 NCH = 8.44E+16 VTH0 = -0.6 +K1 = 4.82E-01 K2 = -2.13E-02 K3 = 8.27E+01 +K3B = -5 W0 = 5.24E-06 NLX = 2.49E-07 +DVT0W = 0.00E+00 DVT1W = 0 DVT2W = 0 +DVT0 = 3.54E-01 DVT1 = 7.52E-01 DVT2 = -2.98E-01 +U0 = 150 UA = 1E-10 UB = 1.75E-18 +UC = -2.27E-11 VSAT = 2.01E+05 A0 = 1.04E+00 +AGS = 2.90E-01 B0 = 1.94E-06 B1 = 5.01E-06 +KETA = -3.85E-03.A1 = 4.20E-03.A2 = 1.00E+00 +RDSW = 4000 PRWG = -9.54E-02 PRWB = -1.92E-03 +WR = 1 WINT = 1.47E-07 LINT = 1.04E-10 +DWG = -1.09E-08 +DWB = 1.14E-08 VOFF = -1.29E-01 NFACTOR = 2.01E+00 +CIT = 0 CDSC = 2.40E-04 CDSCD = 0 +CDSCB = 0 ETA0 = 4.07E-02 ETAB = 6.84E-03 +DSUB = 3.21E-01 PCLM = 5.96E+00 PDIBLC1 = 2.89E-03 +PDIBLC2 = -1.45E-06 PDIBLCB = -1E-03 DROUT = 9.93E-04 +PSCBE1 = 7.88E+10 PSCBE2 = 5E-10 PVAG = 15 +DELTA = 9.96E-03 RSH = 2.6 MOBMOD = 1 +PRT = 0 UTE = -1.5 KT1 = -1.09E-01 +KT1L = 0 KT2 = 2.19E-02 UA1 = 4.34E-09 +UB1 = -7.62E-18 UC1 = -5.63E-11 AT = 3.28E+04 +WL = 0 WLN = 1 WW = 0 +WWN = 1.00E+00 WWL = 0 LL = 0 +LLN = 1 LW = 0 LWN = 1 +LWL = 0 CAPMOD = 2.01E+00 XPART = 0.5 +CGDO = 2.10E-10 CGSO = 2.12E-10 CGBO = 1.00E-12 +CJ = 14e-4 PB = 9.83E-01 MJ = 5.79E-01 +CJSW = 3.2e-10 PBSW = 9.92E-01 MJSW = 3.60E-01 +CJSWG = 4.41E-11 PBSWG = 9.85E-01 MJSWG = 3.58E-01 +CF = 0 PVTH0 = 2.58E-02 PRDSW = -3.98E+01 +PK2 = 2.02E-03 WKETA = 2.72E-03 LKETA = -7.14E-03

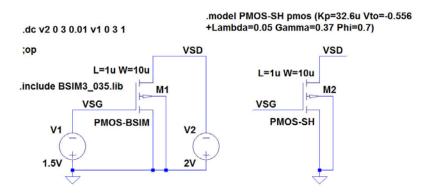

For a PMOS transistor with the transistor model shown in fig. P3.4 (BSIM3 0.35  $\mu$ m model, fig. 3.10) and channel width  $W=10~\mu$ m and channel length  $L=1~\mu$ m, find the bias current  $I_D$  and the small-signal parameters  $g_m$ ,  $g_{mb}$  and  $g_{ds}$  in a bias point of  $V_{SG}=1.5~\rm V$ ,  $V_{BS}=0~\rm V$  and  $V_{SD}=2.0~\rm V$ . From these small-signal parameters and the bias current, estimate parameters for a Shichman-Hodges model for the transistor. Assume  $|2\Phi_F|=0.7~\rm V$ . Simulate and plot the input characteristics ( $I_D$  versus  $V_{SG}$ ) and output characteristics ( $I_D$  versus  $V_{SG}$ ) and output characteristics ( $I_D$  versus  $V_{SG}$ ) and output characteristics

Figure P3.4

### **Solution:**

The figure below shows the schematic for simulating the small-signal parameters and the resulting error log file with the relevant parameters underlined.

| Semicondu | ctor Device | Operating | Points:     |  |

|-----------|-------------|-----------|-------------|--|

|           |             | BSI       | IM3 MOSFETS |  |

| Name:     | m1          |           |             |  |

| Model:    | pmos-bsim   |           |             |  |

| Id:       | -1.60e-04   |           |             |  |

| Vgs:      | -1.50e+00   |           |             |  |

| Vds:      | -2.00e+00   |           |             |  |

| Vbs:      | 0.00e+00    |           |             |  |

| Vth:      | -6.79e-01   |           |             |  |

| Vdsat:    | -6.96e-01   |           |             |  |

| Gm:       | 3.39e-04    |           |             |  |

| Gds:      | 7.31e-06    |           |             |  |

| Gmb       | 7.54e-05    |           |             |  |

|           |             |           |             |  |

teristics ( $I_D$  versus  $V_{SD}$ ).

From the small-signal parameters, the following Shichman-Hodges model parameters are calculated. Beware of the signs. For a PMOS transistor, the easiest solution is to use numeric values in the equations (3.12) to (3.15) in 'CMOS Integrated Circuit Simulation with LTspice – a Tutorial Guide'. Remember that the threshold voltage is negative for a PMOS transistor.

$$\lambda = \frac{g_{ds}}{|I_D| - g_{ds}|V_{DS}|} = 0.05 \text{ V}^{-1}$$

$$V_{to} = -\left(|V_{GS}| - \frac{2|I_D|}{g_m}\right) = -0.556 \text{ V}$$

$$K_p = \left(\frac{g_m}{|I_D|}\right)^2 \left(\frac{|I_D| - g_{ds}|V_{DS}|}{2(W/L)}\right) = 32.6 \text{ } \mu\text{A/V}^2$$

$$|2\Phi_F| = 0.7 \text{ V}$$

$$\gamma = 2\sqrt{|2\Phi_F|} \frac{g_{mb}}{g_m} = 1.67 \frac{g_{mb}}{g_m} = 0.37 \text{ } \sqrt{\text{V}}$$

For simulating the input characteristics and the output characteristics for both the BSIM3 transistor model and the Shichman-Hodges transistor model, the schematic shown below is used. The '.dc' command specification shown gives the output characteristics. For the input characteristics, use V1 as the first source and V2 as the second source.

The simulations result in the characteristics shown below with the green curves for the BSIM3 model and the blue curves for the Shichman-Hodges model.

.MODEL NMOS-BSIM NMOS LEVEL = 49 +VERSION = 3.1 TNOM = 27 TOX = 7.8E-9 +XJ = 1E-07 NCH = 2.18E+17 VTH0 = 0.48 +K1 = 6.07E-01 K2 = 1.24E-03 K3 = 9.68E+01 +K3B = -9.84E+00 W0 = 2.02E-05 NLX = 1.62E-07 +DVT0W = 0 DVT1W = 0 DVT2W = 0 +DVT0 = 2.87E+00 DVT1 = 5.86E-01 DVT2 = -1.26E-01 +U0 = 360 UA = -8.48E-10 UB = 2.27E-18 +UC = 3.27E-11 VSAT = 1.87E+05 A0 = 1.22E+00 +AGS = 2.06E-01 B0 = 9.60E-07 B1 = 4.95E-06 +KFTA = -1 67F-04 A1 = 0 A2 = 3 49F-01 +RDSW = 8.18E+02 PRWG = 2.35E-02 PRWB = -8.12E-02 +WR = 9.98E-01 WINT = 1.55E-07 LINT = 4.51E-10 +DWG = -4 27F-09 +DWB = 4.07E-09 VOFF = -4.14E-02 NFACTOR = 1.61E+00 +CIT = 0 CDSC = 2.39E-04 CDSCD = 0.00E+00 +CDSCB = 0 ETA0 = 1 ETAB = -1.99E-01 +DSUB = 1 PCLM = 1.32E+00 PDIBLC1 = 2.42E-04 +PDIBLC2 = 8.27E-03 PDIBLCB = -9.99E-04 DROUT = 9.72E-04 +PSCBE1 = 7.24E+08 PSCBE2 = 9.96E-04 PVAG = 1.00E-02 +DELTA = 1.01E-02 RSH = 3.33E+00 MOBMOD = 1 +PRT = 0 UTE = -1.5 KT1 = -1.11E-01 +KT1L = 0 KT2 = 2.22E-02 UA1 = 4.34E-09 +UB1 = -7.56E-18 UC1 = -5.62E-11 AT = 3.31E+04 +WL = 0 WLN = 9.95E-01 WW = 0 +WWN = 1.00E+00 WWL = 0 LL = 0 +LLN = 1 LW = 0 LWN = 1 +LWL = 0 CAPMOD = 2 XPART = 0.5 +CGDO = 2.76E-10 CGSO = 2.76E-10 CGBO = 1.00E-12 +CJ = 9e-4 PB = 7.95E-01 MJ = 3.53E-01 +CJSW = 2.8e-10 PBSW = 7.98E-01 MJSW = 1.73E-01 +CJSWG = 1.81E-10 PBSWG = 7.96E-01 MJSWG = 1.74E-01 +CF = 0 PVTH0 = -1.80E-02 PRDSW = -7.56E+01 +PK2 = 4.48E-05 WKETA = -1.33E-03 LKETA = -8.91E-03

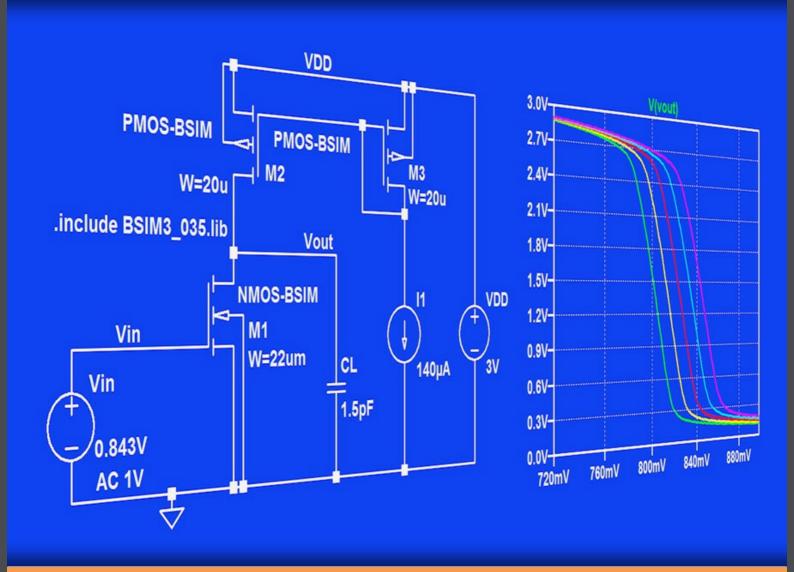

For an NMOS transistor with the transistor model shown in fig. P3.5 (BSIM3 0.35  $\mu$ m model, fig. 3.10), a channel width W=10  $\mu$ m and channel length L=1  $\mu$ m, assume a bias point specified by  $V_{GS}=V_{DS}, V_{SB}=0$  V and  $I_D=140$   $\mu$ A. Find  $g_m$ ,  $g_{mb}$  and  $g_{ds}$  from a '.op' simulation and estimate parameters  $K_p$ ,  $V_{to}$ ,  $\lambda$  and  $\gamma$  for a Shichman-Hodges model for the transistor. Assume  $|2\Phi_F|=0.7$  V.

Figure P3.5

### **Solution:**

The figure below shows the schematic for simulating the small-signal parameters and the resulting error log file with the relevant parameters underlined.

| Semicondi      | actor Device | Operating Points: |

|----------------|--------------|-------------------|

|                |              | BSIM3 MOSFETS     |

| Name:          | m1           |                   |

| Model:         | nmos-bsim    |                   |

| <pre>Id:</pre> | 1.40e-04     |                   |

| Vgs:           | 9.99e-01     |                   |

| Vds:           | 9.99e-01     |                   |

| Vbs:           | 0.00e+00     |                   |

| Vth:           | 5.43e-01     |                   |

| Vdsat:         | 3.36e-01     |                   |

| Gm:            | 5.84e-04     |                   |

| Gds:           | 6.04e-06     |                   |

| Gmb            | 1.67e-04     |                   |

|                |              |                   |

From the small-signal parameters, the following Shichman-Hodges model parameters are calculated using equations (3.12) to (3.15) in 'CMOS Integrated Circuit Simulation with LTspice – a Tutorial Guide'.

$$\lambda = \frac{g_{ds}}{I_D - g_{ds}V_{DS}} = 0.045 \text{ V}^{-1}$$

$$V_{to} = V_{GS} - \frac{2I_D}{g_m} = 0.520 \text{ V}$$

$$K_p = \left(\frac{g_m}{I_D}\right)^2 \left(\frac{I_D - g_{ds}V_{DS}}{2(W/L)}\right) = 117 \text{ } \mu\text{A/V}^2$$

$$|2\Phi_F| = 0.7 \text{ V}$$

$$\gamma = 2\sqrt{|2\Phi_F|} \frac{g_{mb}}{g_m} = 1.67 \frac{g_{mb}}{g_m} = 0.48 \text{ } \sqrt{\text{V}}$$

$$K_p = 190 \ \mu \text{A/V}^2, V_{to} = 0.57 \ \text{V}, \ \lambda = 0.16 \ \text{V}^{-1},$$

$$\gamma = 0.5 \ \sqrt{\text{V}}, \ |2\Phi_F| = 0.7 \ \text{V}.$$

Figure P3.6

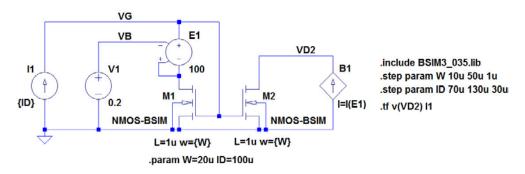

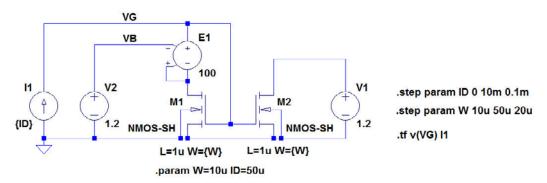

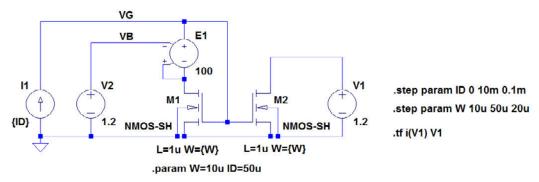

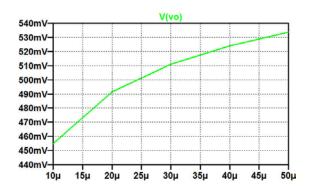

For an NMOS transistor with the Shichman-Hodges parameters shown in fig. P3.6 and a channel length  $L=1~\mu m$ , simulate and plot  $g_m$  and  $g_{ds}$  versus the drain current  $I_D$  for  $W=10~\mu m$ ,  $W=30~\mu m$  and  $W=50~\mu m$ , and  $0<I_D<10~mA$ . Assume a drain-source voltage of  $V_{DS}=1.2~\rm V$ .

From the plots of  $g_m$  and  $g_{ds}$ , find the maximum drain current for which the transistor is in the active region for each of the three values of channel width.

# **Solution:**

For simulating the small-signal parameters  $g_m$  and  $g_{ds}$ , we use a circuit similar to the circuit shown in fig. 3.29 in 'CMOS Integrated Circuit Simulation with LTspice – a Tutorial Guide'. For convenience, fig. 3.29 is shown below.

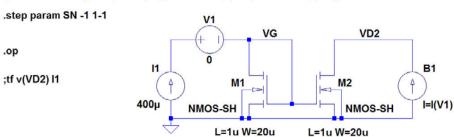

Figure 3.29: NMOS current mirror with voltage buffer for the drain voltage for simulating both  $g_{ds}$  and  $g_m$ .

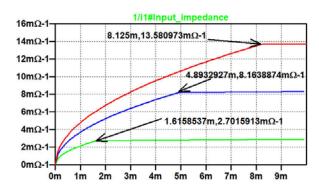

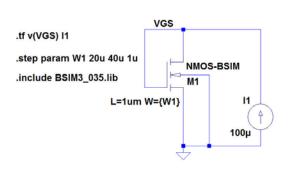

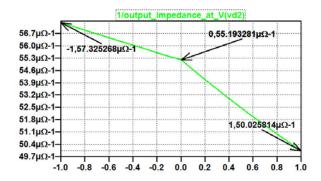

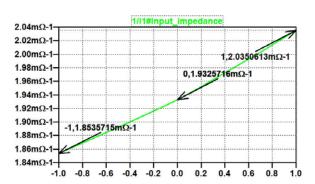

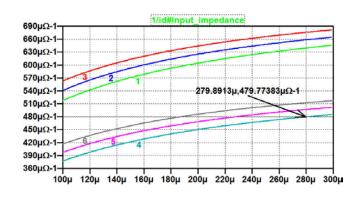

The circuit from fig. 3.29 is modified by replacing the controlled current source for  $M_2$  by a constant voltage of 1.2 V in order to obtain a constant  $V_{DS}$  for the simulation of  $g_{ds}$ . Two '.step param' commands are inserted, one for ID and one for W. The '.step' command for ID is inserted first in order to define ID as the first parameter to step, i.e. defining the x-axis in the output plot from the simulation. In order to simulate  $g_m$ , we run a '.tf' simulation with I1 as the source and v(VG) as the output, see the figure on the following page. From this simulation,  $g_m$  is found as the reciprocal of the input impedance as also shown on the next page. The green curve is for  $W=10~\mu m$ , the blue curve is for  $W=30~\mu m$ , and the red curve is for  $W=50~\mu m$ . Clearly, there is a kink in each of the curves, indicating the limit between

the active region (small values of drain current) and the triode region (large values of drain current).

In the active region,  $g_m$  is found from

$$g_m = \sqrt{2\mu_n C_{ox} \left(\frac{W}{L}\right) I_D (1 + \lambda V_{DS})}$$

showing a square root dependency on  $I_D$  (Equation (3.8) in 'CMOS Integrated Circuit Simulation with LTspice – a Tutorial Guide').

In the triode region,  $g_m$  is found from

$$g_m = \mu_n C_{ox} \left( \frac{W}{L} \right) V_{DS} (1 + \lambda V_{DS})$$

showing that  $g_m$  does not depend on  $I_D$  (Equation (3.11) in 'CMOS Integrated Circuit Simulation with LTspice – a Tutorial Guide').

From the kinks, we find the following maximum values of drain current for which the transistor is in the active region:

$$W = 10 \ \mu \text{m}$$

:  $I_{D \text{max}} = 1.62 \ \text{mA}$ ;  $W = 30 \ \mu \text{m}$ :  $I_{D \text{max}} = 4.89 \ \text{mA}$ ;  $W = 50 \ \mu \text{m}$ :  $I_{D \text{max}} = 8.13 \ \text{mA}$ .

.model NMOS-SH nmos (Kp=190u Vto=0.57 Lambda=0.16 Gamma=0.5 Phi=0.7)

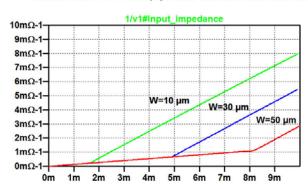

In order to simulate  $g_{ds}$ , we run a '.tf' simulation with V1 as the source and i(V1) as the output, see the figure below. From this simulation,  $g_{ds}$  is found as the reciprocal of the input impedance as shown below. Again, clear kinks are seen, indicating the limit between the active region and the triode region.

.model NMOS-SH nmos (Kp=190u Vto=0.57 Lambda=0.16 Gamma=0.5 Phi=0.7)

# Tutorial 4 – Basic Gain Stages

# 4.1

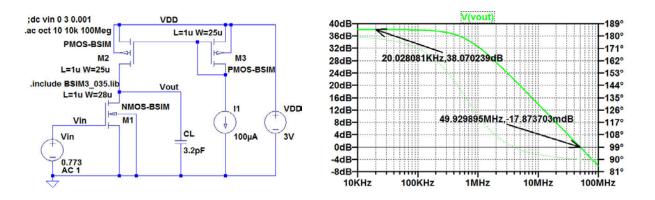

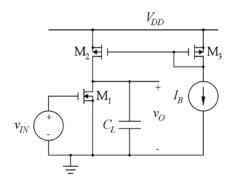

$W_2 = W_3 = 25 \text{ } \mu\text{m}, L_1 = L_2 = L_3 = 1 \text{ } \mu\text{m}$  $C_L = 3.2 \text{ pF}, V_{DD} = 3 \text{ V}, I_B = 100 \text{ } \mu\text{A}.$

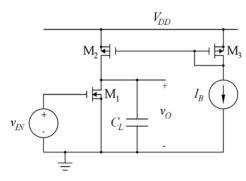

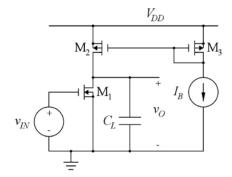

Figure P4.1

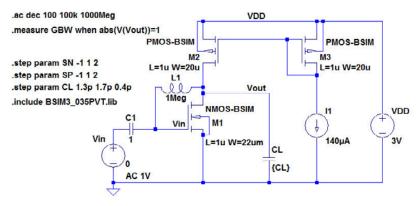

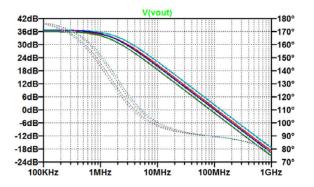

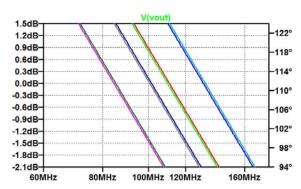

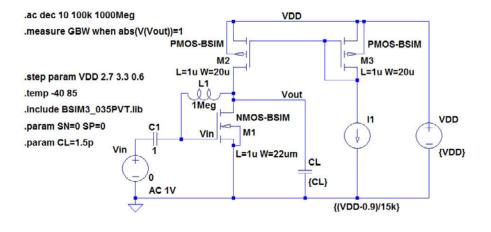

For the common-source amplifier shown in fig. P4.1, design  $M_1$  so the gain-bandwidth product of the stage is 50 MHz. Assume a transistor model as specified in fig. P3.2 on page 98 and fig. P3.3 on page 99 and use a channel length of  $L_1 = 1 \mu m$ . Use a channel width for  $M_1$  which is a multiple of 1  $\mu$ m. Hint: Design M<sub>1</sub> to have the required  $g_m$  for the gain-bandwidth product with  $I_D = 100 \mu A$ . Find  $g_m$ versus  $I_D$  using the method shown in example 3.5 on page 90. Find the dc bias value of the input voltage for which the output voltage is 1.5 V and find the small-signal voltage gain  $A_{\nu}$  at low frequencies.

Figs. P3.2 and P3.3 are shown on page 31 and 33, respectively, in this book.

# **Solution:**

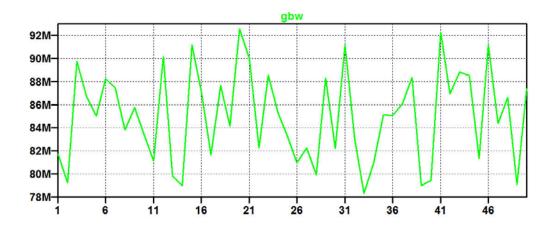

From  $2\pi GBW = g_{m1}/C_L$ , we find  $g_{m1} = 1.0$  mA/V. In order to find a transistor channel width giving this value of  $g_m$ , we run the simulation shown below. From this, we find  $W_1 = 28 \mu m$ .

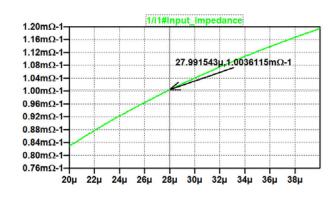

With  $W_1 = 28 \mu m$ , the common-source amplifier is shown in the figure below with a specification for a '.dc' simulation. From the resulting simulation, we find an input bias voltage of  $V_{IN} = 0.773 \text{ V}$  for an output bias voltage of 1.5 V.

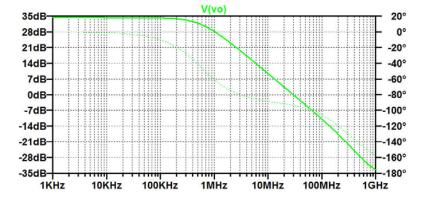

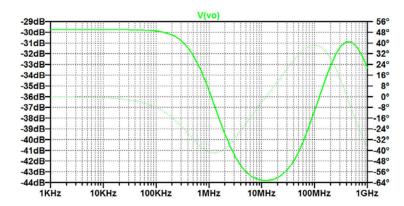

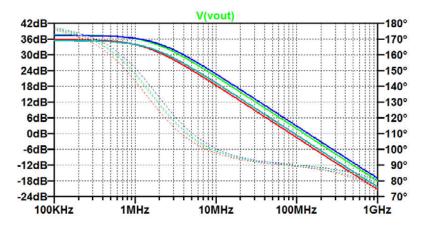

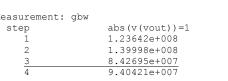

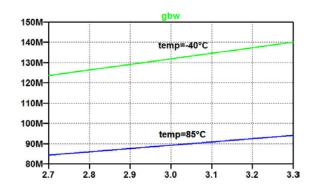

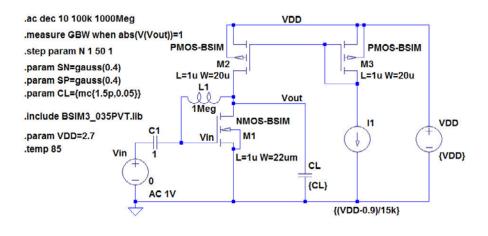

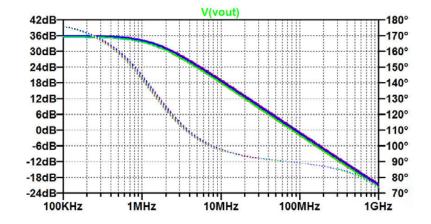

With the bias value for Vin inserted and with an ac amplitude of 1 V for Vin, a '.ac' simulation will show both the gain at low frequencies and verify the gain-bandwidth product of 50 MHz. The figures below show the schematic and the resulting simulation plot. From the plot, we find a low-frequency gain of 38 dB and a gain-bandwidth product of 50 MHz, found as the frequency where the gain has dropped to 0 dB.

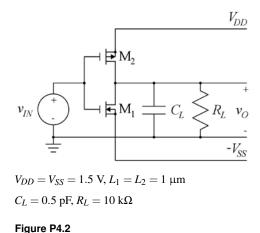

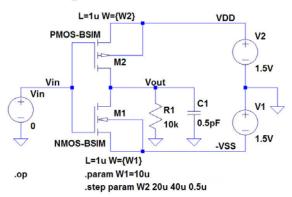

For the inverting amplifier shown in fig. P4.2, design  $M_1$  and  $M_2$  so that the dc bias value of the output voltage is within the range  $\pm 100$  mV with an input dc bias voltage of 0 V and so that the low-frequency small-signal gain with an input dc bias voltage of 0 V is -10 V/V. Assume transistor models as specified in fig. P3.2 on page 98 and fig. P3.3 on page 99 and use a channel length of  $L_1 = L_2 =$ 1  $\mu m$ . Use channel widths for  $M_1$  and  $M_2$  which are multiples of 0.5  $\mu$ m. What is the low-frequency small-signal gain if the load resistor  $R_L$  is omitted? What is the gain-bandwidth product of the amplifier for  $R_L = 10 \text{ k}\Omega$  and for  $R_L = \infty$ ?

Figs. P3.2 and P3.3 are shown on page 31 and 33, respectively in this book.

# **Solution:**

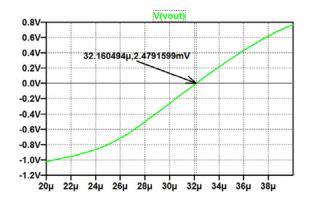

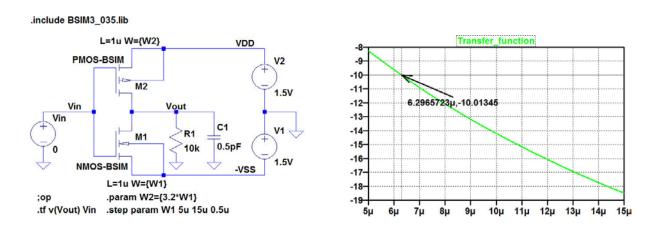

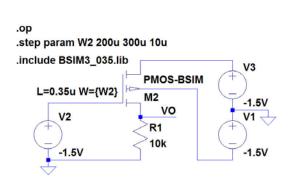

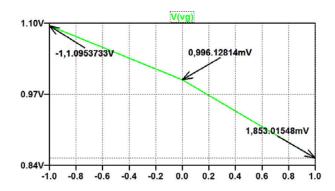

We start the solution by finding a ratio between the channel widths for the NMOS transistor  $(M_1)$  and the PMOS transistor  $(M_2)$ . For this, we may run a simulation as shown below where the channel widths are defined as parameters. The width  $W_1$  is selected to be 10  $\mu$ m while the width  $W_2$  is stepped from  $2W_1$  (20  $\mu$ m) to  $4W_1$  (40  $\mu$ m). From a '.op' simulation, the output voltage is plotted versus  $W_2$ . The plot below shows that with  $W_1 = 10 \mu$ m,  $W_2$  should be 32  $\mu$ m in order to obtain an output voltage of 0 V. Thus, the ratio between  $W_2$  and  $W_1$  is 3.2.

# .include BSIM3\_035.lib

Next, we define the parameter W2 to be 3.2 times the parameter W1 and we step the parameter W1 over a suitable range (5  $\mu$ m to 15  $\mu$ m) and run a '.tf' simulation in order to find the low-frequency gain as a function of  $W_1$ , see figures below. From the simulation plot, we find that in order to obtain a gain of -10 V/V,  $W_1$  should be 6.3  $\mu$ m. Nearest multiple of 0.5  $\mu$ m is  $W_1 = 6.5 \mu$ m, and with this value of  $W_1$ , we find  $W_2 = 3.2 W_1 = 20.8 \mu$ m. Rounding off to nearest multiple of 0.5  $\mu$ m gives  $W_2 = 21 \mu$ m.

With  $W_1 = 6.5 \mu m$  and  $W_2 = 21 \mu m$ , we run a '.op' simulation to verify the bias value of the output voltage and a '.tf' simulation to verify the gain.

The outputs of these simulations are shown below, and we find results reasonably close to the design targets.

| (        | Operating Point |         | Transfer Function            |          |           |

|----------|-----------------|---------|------------------------------|----------|-----------|

| V(vout): | 0.0203095       | voltage | Transfer function:           | -10.2859 | transfer  |

| V(vin):  | 0               | voltage | vin#Input_impedance:         | 1e+020   | impedance |

| V(vdd):  | 1.5             | voltage | output_impedance_at_V(vout): | 7651.2   | impedance |

| V(-vss): | -1.5            | voltage |                              |          |           |

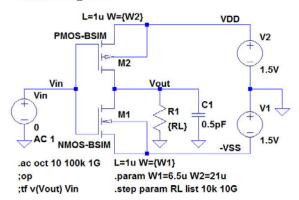

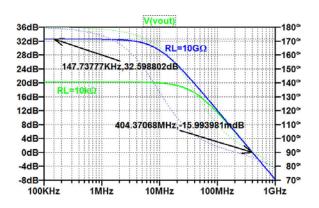

Finally, in order to find low-frequency gain and gain-bandwidth product for  $R_L = 10 \text{ k}\Omega$  and  $R_L = \infty$ , we run a '.ac' simulation with  $R_L$  stepped between two values, 10k and 10G. From the simulation plot on the following page, we find that with  $R_L = \infty$  (10G), the low-frequency gain is 32.6 dB (or -43.6 V/V), and the gain-bandwidth product is 404 MHz, independent of  $R_L$ .

#### .include BSIM3\_035.lib

In order to verify that the '.ac' simulation runs from a reasonable bias point, also when  $R_L = \infty$ , a '.op' simulation with RL=10G may be run. The output file from this simulation is shown below, confirming that the bias value of  $V_O$  is less than 100 mV.

--- Operating Point ---

| V(vout): | 0.0856978 | voltage |

|----------|-----------|---------|

| V(vin):  | 0         | voltage |

| V(vdd):  | 1.5       | voltage |

| V(-vss): | -1.5      | voltage |

# TURN TO THE EXPERTS FOR SUBSCRIPTION CONSULTANCY

Subscrybe is one of the leading companies in Europe when it comes to innovation and business development within subscription businesses.

We innovate new subscription business models or improve existing ones. We do business reviews of existing subscription businesses and we develope acquisition and retention strategies.

Learn more at linkedin.com/company/subscrybe or contact Managing Director Morten Suhr Hansen at mha@subscrybe.dk

SUBSCRYBE - to the future

$L_1 = L_2 = L_3 = L_4 = L_5 = L_6 = L_7 = L_8 = 0.35 \ \mu m$  $R_L = 10 \ k\Omega, V_{DD} = V_{SS} = 1.5 \ V.$

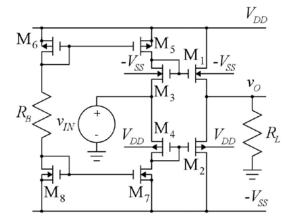

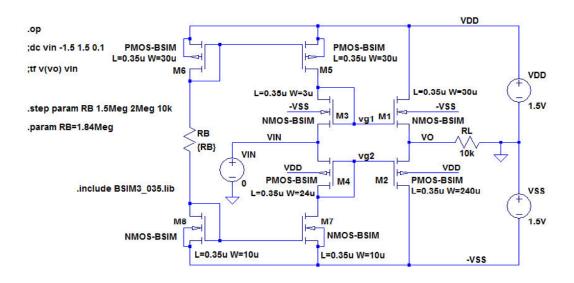

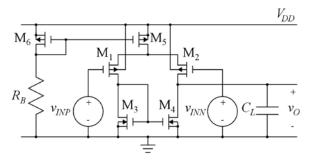

Figure P4.3

Fig. P4.3 shows a class AB buffer amplifier. Design the output transistors  $M_1$  and  $M_2$  so that the amplifier can deliver an output voltage swing of  $\pm 0.5 \text{ V}$ with a load resistor of 10 k $\Omega$ . Assume that the gate voltage of M<sub>1</sub> and M<sub>2</sub> can reach the positive and negative supply voltages, respectively. Select values of the channel widths which are multiples of 10 µm. Use transistor models as specified in fig. P3.2 on page 98 and fig. P3.3 on page 99. Design the bias network M<sub>3</sub> - M<sub>8</sub> and  $R_B$  to provide a bias current of 1  $\mu$ A for  $M_3$  -  $M_8$ .  $M_5$  -  $M_8$  should be designed to have a saturation voltage  $|V_{DSsat}|$  of less than 50 mV, and the channel widths should be multiples of 10 μm. M<sub>3</sub> and M<sub>4</sub> should be scaled to channel widths of 0.1 times the channel widths of  $M_1$  and  $M_2$ , respectively. Plot the output voltage versus the input voltage for  $-1.5 \text{ V} < v_{IN} < 1.5 \text{ V}$ . Find the open circuit voltage gain and the output resistance of the buffer for an input bias voltage of 0 V. Find the bias current in M<sub>1</sub> and M<sub>2</sub> for an output bias voltage of  $V_O = 0$  V. Why is the current scaling in M1 - M2 / M3 - M4 different from the channel width scaling?

# **Solution:**

For finding the channel width  $W_1$ , we run a '.op' simulation on a single NMOS transistor with gate, source, drain and bulk connected to voltages resulting in the highest value of output voltage. Using a '.step param' directive, the output voltage is simulated versus the channel width. The figure below shows the schematic and the simulation plot from which we find  $W_1 = 30 \mu m$  (using multiples of 10  $\mu m$ ) in order to achieve an output voltage of +0.5 V.

The channel width  $W_2$  is found in the same way as  $W_1$ , running a '.op' simulation on a single PMOS transistor with gate, source, drain and bulk connected to voltages resulting in the lowest value of output voltage. The figure below shows the schematic and the simulation plot from which we find  $W_2 = 240 \,\mu\text{m}$  (using multiples of 10  $\mu$ m) in order to achieve an output voltage of  $-0.5 \,\text{V}$ .

For the bias network,  $M_3$  and  $M_4$  are designed by scaling  $W_1$  and  $W_2$  by a factor of 10, respectively. This gives  $W_3 = 3 \mu m$  and  $W_4 = 24 \mu m$ .

The transistors  $M_5$  -  $M_8$  should have a saturation voltage of less than 50 mV for a drain current of 1  $\mu$ A.

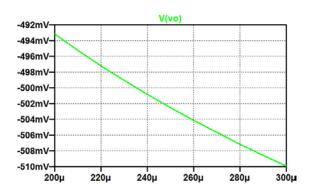

For the PMOS transistors ( $M_5$  and  $M_6$ ), the channel width is found from the simulation shown in the figure below. The simulation is run with different values of  $W_5$  in multiples of 10  $\mu$ m and the smallest value of  $W_5$  resulting in  $|V_6| = 10$  mV is selected, i.e.  $W_5 = W_6 = 30$   $\mu$ m.

| Semicondu | ctor Device | Operating Pos |         |  |

|-----------|-------------|---------------|---------|--|

| Name:     | m.5         | B2IM3         | MOSFETS |  |

|           |             |               |         |  |

| Model:    | pmos-bsim   |               |         |  |

| Id:       | -1.00e-06   |               |         |  |

| Vgs:      | -6.25e-01   |               |         |  |

| Vds:      | -6.25e-01   |               |         |  |

| Vbs:      | 0.00e+00    |               |         |  |

| Vth:      | -7.26e-01   |               |         |  |

| Vdsat.    | -4 87e-02   |               |         |  |

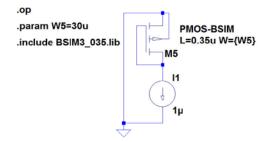

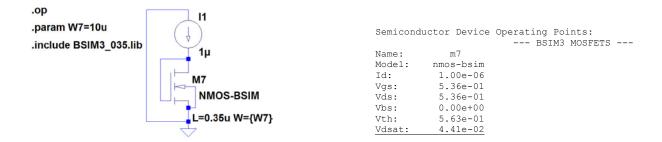

For the NMOS transistors ( $M_7$  and  $M_8$ ), the channel width is found from the simulation shown in the figure below. The simulation is run with different values of  $W_7$  in multiples of 10  $\mu$ m and the smallest value of  $W_7$  resulting in  $V_8 = 50$  mV is selected, i.e.  $W_7 = W_8 = 10$   $\mu$ m.

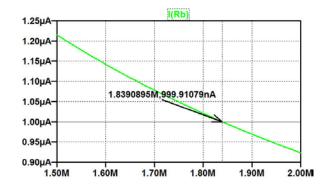

With all transistor dimensions in place, the complete schematic can be drawn as shown below. The only device still to be designed is  $R_B$ . This can be found from a '.op' simulation with RB stepped over a suitable range. From the simulation plot shown below, we find  $R_B = 1.84 \text{ M}\Omega$ .

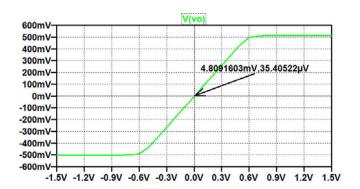

Next, a '.dc' simulation is run, resulting in the simulation plot shown below. For this simulation, the '.step param' directive is changed into a comment and  $R_B$  is defined by the '.param' command shown in the schematic on the previous page.

For finding the open circuit voltage gain and output resistance for an input bias voltage of 0 V, we run a '.tf' simulation with RL disconnected. The output file is shown below, and we find  $A_{voc} = 0.95$  V/V and  $r_o = 1005 \ \Omega$ .

#### --- Transfer Function ---

| Transfer_function:         | 0.951633 | transfer  |

|----------------------------|----------|-----------|

| vin#Input_impedance:       | 674020   | impedance |

| output_impedance_at_V(vo): | 1005.47  | impedance |

For finding the bias currents in  $M_1$  and  $M_2$  for an output voltage of 0 V, we use the '.dc' simulation shown on the previous page to find the value of the input voltage resulting in V(vo) = 0. From the plot, we find an input voltage of 4.809 mV. With this value of VIN, we run a '.op' simulation, and the error log file from this gives all the transistor bias currents as shown below.

| Semicondu | ctor Device | Operating Po | oints:<br>3 MOSFETS | _         |           |

|-----------|-------------|--------------|---------------------|-----------|-----------|

| Name:     | m6          | m5           | m2                  | m4        | m8        |

| Model:    | pmos-bsim   | pmos-bsim    | pmos-bsim           | pmos-bsim | nmos-bsim |

| Id:       | -9.99e-07   | -1.01e-06    | -1.89e-05           | -1.05e-06 | 9.99e-07  |

| Vgs:      | -6.25e-01   | -6.25e-01    | -8.82e-01           | -8.86e-01 | 5.36e-01  |

| Vds:      | -6.25e-01   | -6.35e-01    | -1.50e+00           | -8.86e-01 | 5.36e-01  |

| Vbs:      | 0.00e+00    | 0.00e+00     | 1.50e+00            | 1.50e+00  | 0.00e+00  |

| Vth:      | -7.26e-01   | -7.26e-01    | -9.53e-01           | -9.77e-01 | 5.63e-01  |

| Vdsat:    | -4.87e-02   | -4.87e-02    | -5.94e-02           | -5.54e-02 | 4.41e-02  |

| Name:     | m7          | m3           | m1                  |           |           |

| Model:    | nmos-bsim   | nmos-bsim    | nmos-bsim           |           |           |

| Id:       | 1.05e-06    | 1.01e-06     | 1.89e-05            |           |           |

| Vqs:      | 5.36e-01    | 8.60e-01     | 8.65e-01            |           |           |

| Vds:      | 6.18e-01    | 8.60e-01     | 1.50e+00            |           |           |

| Vbs:      | 0.00e+00    | -1.50e+00    | -1.50e+00           |           |           |

| Vth:      | 5.62e-01    | 8.45e-01     | 8.32e-01            |           |           |

| Vdsat:    | 4.43e-02    | 5.94e-02     | 6.62e-02            |           |           |

Obviously, the current scaling in  $M_1$  -  $M_2$  /  $M_3$  -  $M_4$  is larger than the channel width scaling. This is caused by the larger  $|V_{DS}|$  values for  $M_1$  -  $M_2$  than for  $M_3$  -  $M_4$ , by the input offset voltage, and by the smaller threshold voltages for  $M_1$  -  $M_2$  than for  $M_3$  -  $M_4$ .

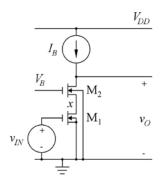

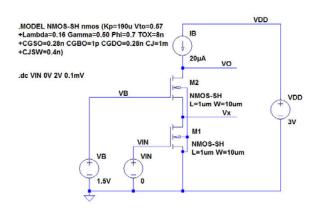

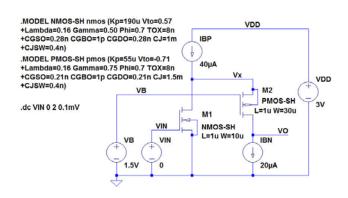

$L_1 = L_2 = 1 \text{ } \mu\text{m}, W_1 = W_2 = 10 \text{ } \mu\text{m}$  $I_B = 20 \text{ } \mu\text{A}, V_B = 1.5 \text{ } V, V_{DD} = 3 \text{ } V.$

.MODEL NMOS-SH nmos (Kp=190u Vto=0.57

- +Lambda=0.16 Gamma=0.50 Phi=0.7 TOX=8n

- +CGSO=0.28n CGBO=1p CGDO=0.28n CJ=1m

- +CJSW=0.4n)

Figure P4.4

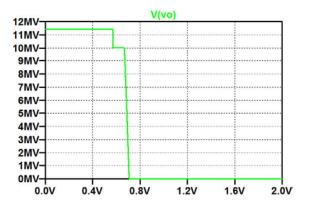

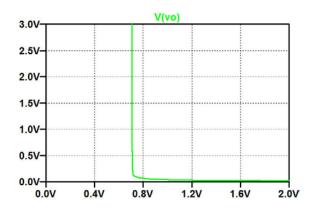

For the telescopic cascode shown in fig. P4.4, find the bias value of  $V_{IN}$  required to give an output voltage of 2 V. Also find the small-signal gain  $A_{voc}$  and output resistance  $r_o$  at low frequencies. Find the small-signal resistance  $r_x$  to ground from the node x between the source of  $M_2$  and the drain of  $M_1$ . Assume a transistor model as shown in fig. P4.4.

# **Solution:**

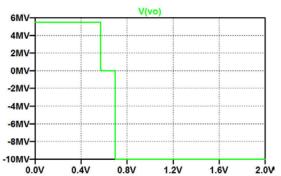

The figure below shows the cascode stage with a specification for a '.dc' simulation. Also shown is the resulting plot of the output voltage. Obviously, the simulation generates unrealistically high output voltages, several MV. This is due to the fact that the drain of  $M_2$  is connected directly to an ideal dc current source.

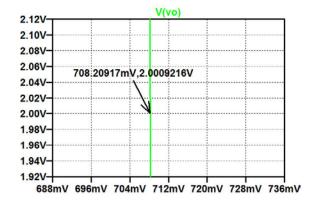

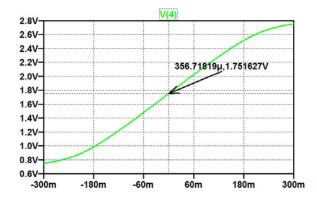

In order to see V(vo) in a realistic range of output voltages, we set the range of the y-axis to 3 V, either by the command 'Plot Settings  $\rightarrow$  Manual Limits' or by moving the cursor to the y-axis and using a left click on the mouse. The resulting plot is shown below, left plot. Obviously, the output voltage changes abruptly for an input voltage of about 0.7 V, and in order to find the exact input voltage, we zoom in on a small part of the plot, see right plot below. From this, we find  $V_{IN} = 708.21$  mV. Notice that this value has been specified with a resolution exceeding the step size in the '.dc' command, so it is based on an interpolation.

In order to verify the bias point, we run a '.op' simulation with a dc value of  $V_{IN}$  specified to 708.21 mV. The output file from this is shown below, and we see that  $V(v_0)$  is sufficiently close to 2 V.

--- Operating Point ---

| 638226 voltage |

|----------------|

| 70821 voltage  |

| 97479 voltage  |

| 5 voltage      |

| voltage        |

|                |

With the bias point in place, the small-signal gain  $A_{voc}$  and output resistance  $r_o$  at low frequencies are found from a '.tf' simulation with V(VO) as the output and VIN as the source. The output file from this '.tf' simulation is shown below. From this, we find a gain of -14065 V/V or 83 dB and an output resistance of 49 M $\Omega$ .

--- Transfer Function ---

| Transfer function:         | -14065.1     | transfer  |

|----------------------------|--------------|-----------|

| vin#Input_impedance:       | 1e+020       | impedance |

| output impedance at V(vo): | 4.89777e+007 | impedance |

For finding the small-signal resistance  $r_x$  to ground from the node x between the source of  $M_2$  and the drain of  $M_1$ , we run a '.tf' simulation with V(Vx) as the output and VIN as the source. The output file from this '.tf' simulation is shown below. From this, we find a resistance  $r_x$  of 344 k $\Omega$ .

--- Transfer Function ---

| Transfer function:         | -99.6727 | transfer  |

|----------------------------|----------|-----------|

| vin#Input impedance:       | 1e+020   | impedance |

| output impedance at V(vx): | 344394   | impedance |

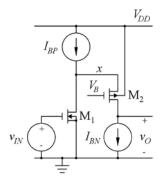

$L_1=L_2=1$  μm,  $W_1=10$  μm,  $W_2=30$  μm  $I_{BP}=40$  μA,  $I_{BN}=20$  μA,  $V_B=1.5$  V,  $V_{DD}=3$  V. .MODEL PMOS-SH pmos (Kp=55u Vto=-0.71 +Lambda=0.16 Gamma=0.75 Phi=0.7 TOX=8n +CGSO=0.21n CGBO=1p CGDO=0.21n CJ=1.5m +CJSW=0.4n)

Figure P4.5

For the folded cascode shown in fig. P4.5, find the bias value of  $V_{IN}$  required to give an output voltage of 1 V. Also find the small-signal gain  $A_{voc}$  and output resistance  $r_o$  at low frequencies. Find the small-signal resistance  $r_x$  to ground from the node x between the source of  $M_2$  and the drain of  $M_1$ . Assume transistor models as shown in fig. P4.4 and P4.5.

# **Solution:**

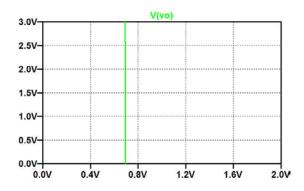

The figure below shows the folded-cascode stage with a specification for a '.dc' simulation. Also shown is the resulting plot of the output voltage. Obviously, the simulation generates unrealistically high output voltages, several MV. This is due to the biasing by two ideal dc current sources. You may also notice that the simulation time is quite long, and examining the error log file, you find that LTspice has some challenges in finding the operating points for the values of input voltage giving unrealistic values of output voltage.

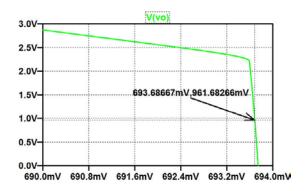

In order to see V(vo) in a realistic range of output voltages, we set the range of the y-axis to 3 V, either by the command 'Plot Settings  $\rightarrow$  Manual Limits' or by moving the cursor to the y-axis and using a left click on the mouse. The resulting plot is shown below, left plot. Obviously, the output voltage changes abruptly for an input voltage of about 0.7 V. Even when zooming in on a small part of the plot, it is difficult to find the value of  $V_{IN}$  resulting in an output voltage of 1 V, so in order to improve the accuracy, we run a '.dc' simulation from 690 mV to 694 mV with a step size of 1  $\mu$ V. From this, we find  $V_{IN} = 693.687$  mV.

**PDF** components for **PHP** developers

www.setasign.com

In order to verify the bias point, we run a '.op' simulation with a dc value of  $V_{IN}$  specified to 693.687 mV. The output file from this is shown below, and we see that V(vo) is sufficiently close to 1 V, and also the voltage at the intermediate node x has a reasonable value within the supply voltage range.

--- Operating Point ---

| V(vx):  | 2.35079  | voltage |

|---------|----------|---------|

| V(vin): | 0.693687 | voltage |

| V(vdd): | 3        | voltage |

| V(vb):  | 1.5      | voltage |

| V(vo):  | 0.95661  | voltage |

With the bias point in place, the small-signal gain  $A_{voc}$  and output resistance  $r_o$  at low frequencies are found from a '.tf' simulation with V(VO) as the output and VIN as the source. The output file from this '.tf' simulation is shown below. From this, we find a gain of -15241 V/V or 84 dB and an output resistance of 48 M $\Omega$ .

--- Transfer Function ---

| Transfer_function:         | -15241.3    | transfer  |

|----------------------------|-------------|-----------|

| vin#Input_impedance:       | 1e+020      | impedance |

| output impedance at V(vo): | 4.7511e+007 | impedance |

For finding the small-signal resistance  $r_x$  to ground from the node x between the source of  $M_2$  and the drain of  $M_1$ , we run a '.tf' simulation with  $\mathbb{V}(\mathbb{V}\mathbb{X})$  as the output and  $\mathbb{V}\mathbb{I}\mathbb{N}$  as the source. The output file from this '.tf' simulation is shown below. From this, we find a resistance  $r_x$  of 430 k $\Omega$ .

--- Transfer Function ---

| Transfer function:         | -139.073 | transfer  |

|----------------------------|----------|-----------|

| vin#Input impedance:       | 1e+020   | impedance |

| output impedance at V(vx): | 430039   | impedance |

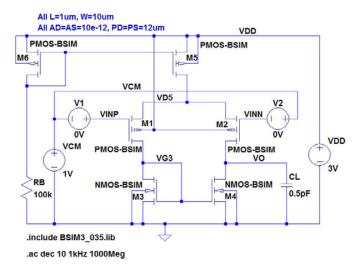

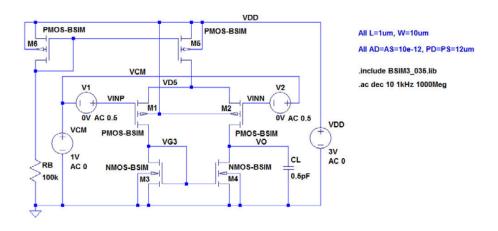

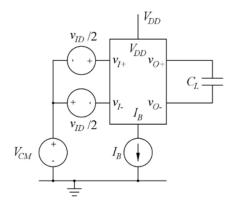

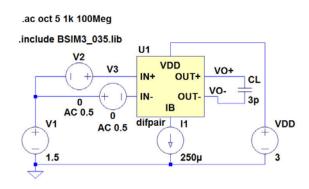

Figure P4.6

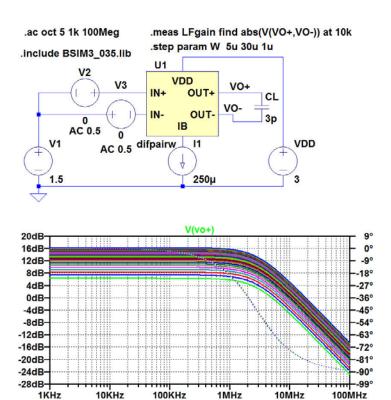

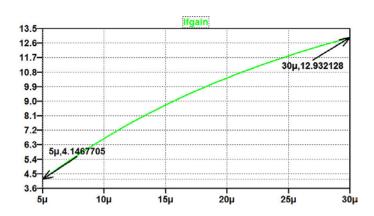

Fig. P4.6 shows an alternative version of the LTspice schematic from fig. 4.21 with a different arrangement for the input voltages. Define the ac amplitudes of VCM, V1, V2 and VDD such that the '.ac' simulation shows the differential gain and compare your simulation to fig. 4.25. Next, define the ac amplitudes of VCM, V1, V2 and VDD such that the '.ac' simulation shows the common-mode gain and compare your simulation to fig. 4.26. Finally, define the ac amplitudes of VCM, V1, V2 and VDD such that the '.ac' simulation shows the power supply rejection and compare your simulation to fig. 4.27.

Rand Merchant Bank uses good business to create a better world, which is one of the reasons that the country's top talent chooses to work at RMB. For more information visit us at www.rmb.co.za

Thinking that can change your world

Rand Merchant Bank is an Authorised Financial Services Provider

For convenience, fig. 4.21 is shown below.

Figure 4.21: LTspice schematic for simulations of a PMOS differential pair with NMOS active load.

# **Solution:**

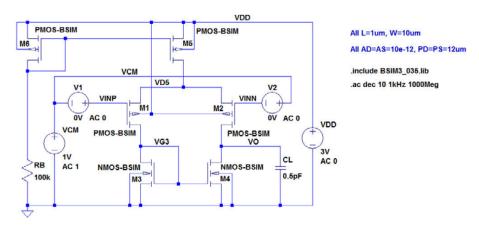

For the differential gain, we define the ac amplitudes in fig. P4.6 as follows:

VCM: AC Amplitude = 0, V1: AC Amplitude = 0.5, V2: AC Amplitude = 0.5, VDD: AC Amplitude = 0. The resulting schematic and simulation plot is shown below. The simulation plot is identical to fig. 4.25 in 'CMOS Integrated Circuit Simulation with LTspice – a Tutorial Guide'.

For the common-mode gain, we define the ac amplitudes in fig. P4.6 as follows: VCM: AC Amplitude = 1, V1: AC Amplitude = 0, V2: AC Amplitude = 0, VDD: AC Amplitude = 0. The resulting schematic and simulation plot is shown below. The simulation plot is identical to fig. 4.26 in 'CMOS Integrated Circuit Simulation with LTspice – a Tutorial Guide'.

For the power supply rejection, we define the ac amplitudes in fig. P4.6 as follows: VCM: AC Amplitude = 0, V1: AC Amplitude = 0, V2: AC Amplitude = 0, VDD: AC Amplitude = 1. The resulting schematic and simulation plot is shown below. The simulation plot is identical to fig. 4.27 in 'CMOS Integrated Circuit Simulation with LTspice – a Tutorial Guide'.

$$L_1 = L_2 = L_3 = L_4 = L_5 = 1$$

μm

$$W_1 = 30$$

μm,  $W_2 = 33$  μm,  $W_3 = W_4 = W_5 = W_6 = 10$  μm

$$AD_1 = AS_1 = AD_2 = AS_2 = 30 \text{ (μm)}^2$$

$$AD_3 = AS_3 = AD_4 = AS_4 = AD_5 = AS_5 = AD_6 = AS_6 = 10 \text{ (μm)}^2$$

$$PD_1 = PS_1 = PD_2 = PS_2 = 32 \text{ μm}$$

$$PD_3 = PS_3 = PD_4 = PS_4 = PD_5 = PS_5 = PD_6 = PS_6 = 12 \text{ μm}$$

$$R_B = 100 \text{ kΩ}, C_L = 0.5 \text{ pF}, V_{DD} = 3.0 \text{ V}, V_{CM} = 1 \text{ V}$$

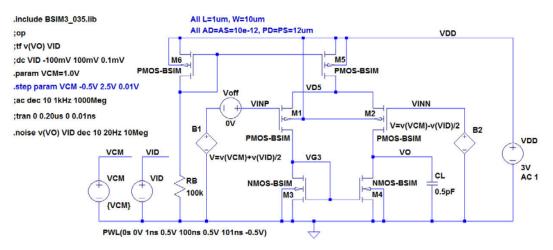

Figure P4.7

For the differential pair shown in fig. P4.7, we assume that a layout error has resulted in a mismatch between  $M_1$  and  $M_2$  such that  $W_1 = 30 \mu m$ and  $W_2 = 33 \mu m$ . Find the input offset voltage caused by this error for a common-mode input voltage of  $V_{CM}$  = 1 V and an output voltage of 0.7 V. Use the Shichman-Hodges transistor model from fig. P4.4 and P4.5. Next, plot the differential gain and the commonmode gain versus frequency. Find the gain-bandwidth product and calculate the common-mode rejection ratio at low frequencies. Also plot the gain from the power supply to the output and calculate the power supply rejection ratio at low frequencies.

Figs. P4.4 and P4.5 are shown on page 55 and 58, respectively, in this book.

Discover the truth at www.deloitte.ca/careers

Deloitte

© Deloitte & Touche LLP and affiliated entities.

# **Solution:**

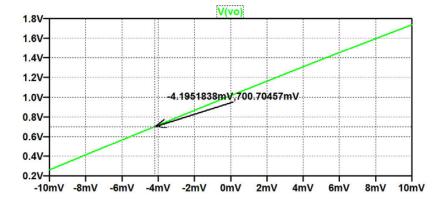

The figure below shows the schematic in LTspice. For finding the offset voltage, we use a '.dc' simulation with the input voltage V1 to the noninverting input as the source to sweep. From the simulation plot below, we find that a dc input voltage of -4.2 mV results in an output voltage of 0.7 V. Thus,  $V_{\text{off}} = -4.2$  mV.

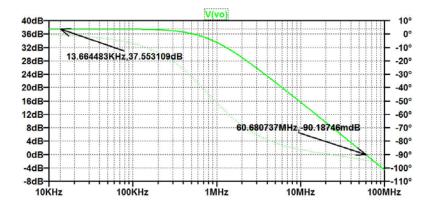

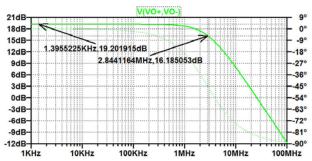

For finding the differential gain, we specify a dc value of -4.2 mV for V1 and an ac amplitude of 0.5 V for both V1 and V2 in the schematic on the previous page. We use a '.ac' simulation with a start frequency of 10 kHz and a stop frequency of 100 MHz: '.ac oct 10 10k 100Meg'. This results in the output plot below where we find the differential low-frequency gain to be 37.6 dB and the gain-bandwidth product to be 60.7 MHz.

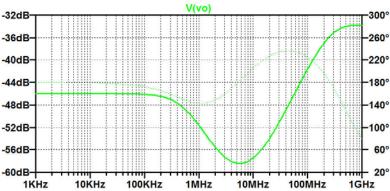

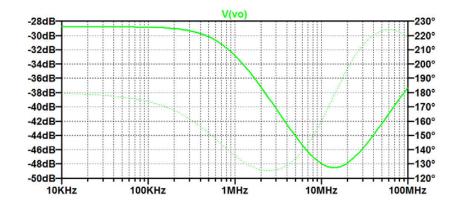

For finding the common-mode gain, we specify a dc value of -4.2 mV for V1 and an ac amplitude of 0 V for both V1 and V2 in the schematic on the previous page. Also, we specify an ac amplitude of 1 V for VCM. We use a '.ac' simulation with a start frequency of 10 kHz and a stop frequency of 100 MHz: '.ac oct 10 10k 100Meg'. This results in the output plot below where we find the common-mode low-frequency gain to be -28.8 dB, so the common-mode rejection ratio is CMRR = 37.6 dB + 28.8 dB = 66.4 dB.

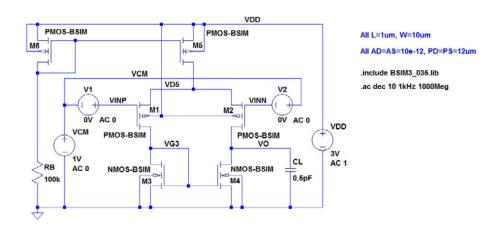

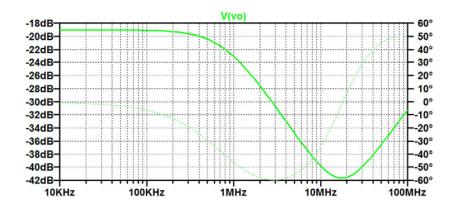

For finding the power supply rejection, we specify a dc value of -4.2 mV for V1 and an ac amplitude of 0 V for both V1, V2 and VCM. Also, we specify an ac amplitude of 1 V for VDD. We use a '.ac' simulation with a start frequency of 10 kHz and a stop frequency of 100 MHz: '.ac oct 10 10k 100Meg'. This results in the output plot below where we find the power supply rejection at low frequency to be 19.0 dB, so the power supply rejection ratio is PSRR = 37.6 dB + 19.0 dB = 56.6 dB

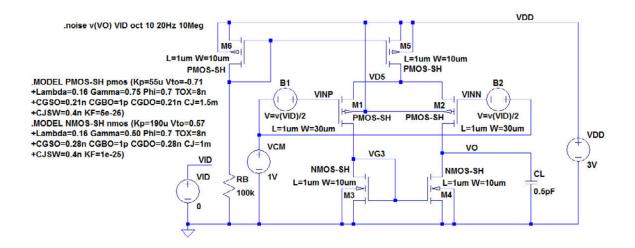

.MODEL PMOS-SH pmos (Kp=55u Vto=-0.71 +Lambda=0.16 Gamma=0.75 Phi=0.7 TOX=8n +CGSO=0.21n CGBO=1p CGDO=0.21n CJ=1.5m +CJSW=0.4n KF=5e-26) .MODEL NMOS-SH nmos (Kp=190u Vto=0.57 +Lambda=0.16 Gamma=0.50 Phi=0.7 TOX=8n +CGSO=0.28n CGBO=1p CGDO=0.28n CJ=1m +CJSW=0.4n KF=1e-25)

Figure P4.8

For the differential pair shown in fig. P4.7 with  $W_1 = W_2 = 30 \mu m$ , assume the transistor models shown in fig. P4.8 which include parameters for the flicker noise modelling. Plot the total noise spectral density of the output voltage and the noise contributions from  $M_1$  and  $M_3$  in the frequency range 20 kHz to 10 MHz, using logarithmic axes. Find the total rms output noise voltage in this frequency range. Also plot the input referred noise spectral density and find the total rms input referred noise voltage in this frequency range.

# **Solution:**

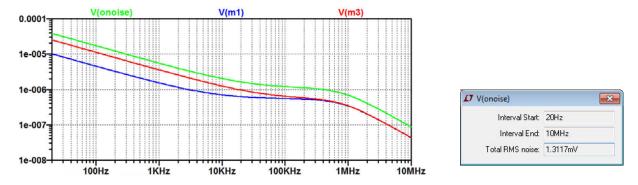

The figure below shows the schematic in LTspice. For finding the noise voltage, we use a '.noise' simulation with VID as the input and v(VD) as the output.

When plotting the noise contribution, remember to change the y-axis to logarithmic scale and use reasonable top and bottom limits. The output voltage is selected by pointing to the output node. The noise contributions from transistors  $M_1$  and  $M_3$  are selected by pointing to the transistors. The total output noise voltage is found by pointing to the green label 'V(onoise)' above the plot and using a 'Ctrl-left click'. This opens the information window shown below, and we find  $V_{on\,(rms)}=1.3$  mV.

The input referred spectral noise density is selected in the plot window by the command 'Plot Settings  $\rightarrow$  Visible Traces' and is shown below together with the information window resulting from a 'Ctrl-left click' on the label above the plot. We find a total equivalent input noise of  $V_{in(rms)} = 48 \mu V$ .

# Tutorial 5 – Hierarchical Design

5.1

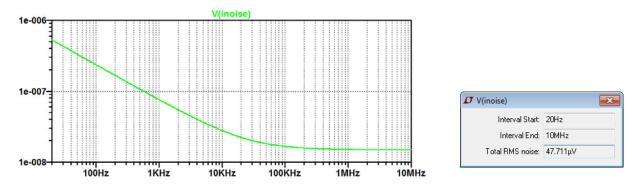

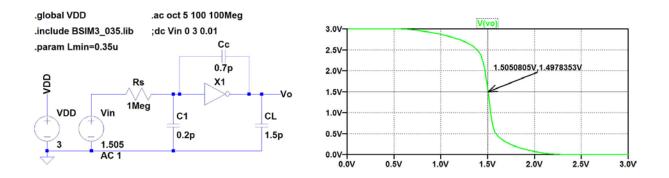

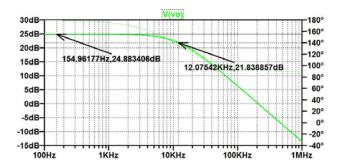

$R_s = 1 \text{ M}\Omega, V_{DD} = 3 \text{ V},$  $C_1 = 0.2 \text{ pF}, C_c = 0.7 \text{ pF}, C_L = 1.5 \text{ pF}.$

Figure P5.1

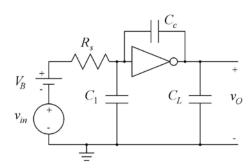

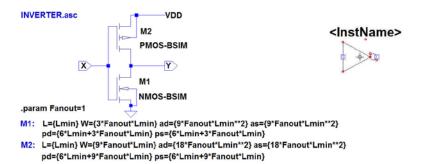

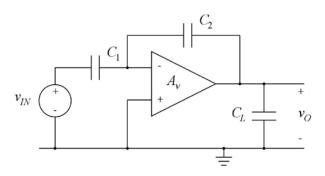

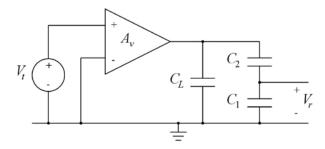

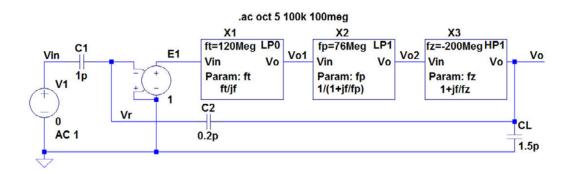

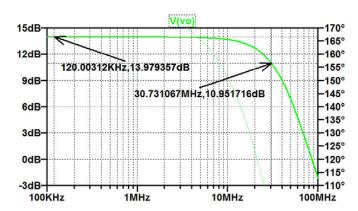

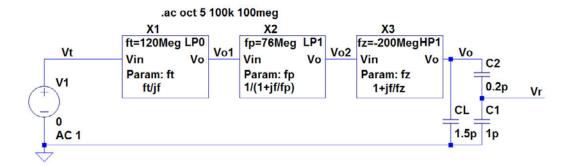

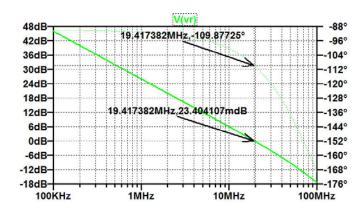

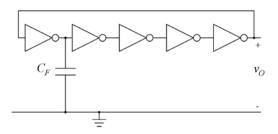

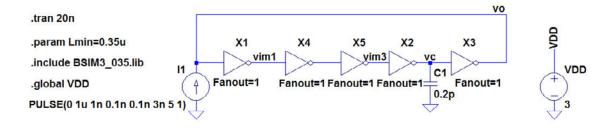

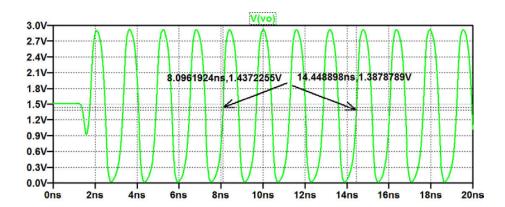

An inverter as shown in fig. 5.25 on page 170 may be used as an inverting amplifier. Design a test bench as shown in fig. P5.1 using a supply voltage of 3 V, a minimum length of Lmin=0.35u, a fanout of Fanout=1 and the BSIM3 transistor model from fig. 3.10 on page 77. Find a bias input voltage  $V_B$  which gives a bias output voltage of 1.5 V. With this value of  $V_B$ , simulate the ac response and find the dominant pole. Also, use the Miller approximation (Chan Carusone, Johns & Martin 2012) to calculate the dominant pole and compare to the simulated value.

For convenience, figs. 5.25 and 3.10 are shown below.

Figure 5.25: Inverter, schematic and symbol.

```

Generic BSIM3 model for 0.35 μm CMOS process. Adapted from (Chan Carusone, Johns & Martin 2014).

.MODEL NMOS-BSIM NMOS LEVEL = 49

.MODEL PMOS-BSIM PMOS LEVEL = 49

+VERSION = 3.1 TNOM = 27 TOX = 7.8E-9

+VERSION = 3.1 TNOM = 2.69E+01 TOX = 7.8E-9

+XJ = 1E-07 NCH = 2.18E+17 VTH0 = 0.48

+XJ = 1.00E-07 NCH = 8.44E+16 VTH0 = -0.6

+K1 = 6.07E-01 K2 = 1.24E-03 K3 = 9.68E+01

+K1 = 4.82E-01 K2 = -2.13E-02 K3 = 8.27E+01

+K3B = -9.84E+00 W0 = 2.02E-05 NLX = 1.62E-07

+K3B = -5 W0 = 5.24E-06 NLX = 2.49E-07

+DVT0W = 0 DVT1W = 0 DVT2W = 0

+DVT0W = 0.00E+00 DVT1W = 0 DVT2W = 0

+DVT0 = 2.87E+00 DVT1 = 5.86E-01 DVT2 = -1.26E-01

+DVT0 = 3.54E-01 DVT1 = 7.52E-01 DVT2 = -2.98E-01

+U0 = 360 UA = -8.48E-10 UB = 2.27E-18

+U0 = 150 UA = 1E-10 UB = 1.75E-18

+UC = 3.27E-11 VSAT = 1.87E+05 A0 = 1.22E+00

+UC = -2.27E-11 VSAT = 2.01E+05 A0 = 1.04E+00

+AGS = 2.06E-01 B0 = 9.60E-07 B1 = 4.95E-06

+AGS = 2.90E-01 B0 = 1.94E-06 B1 = 5.01E-06

+KETA = -1.67E-04 A1 = 0 A2 = 3.49E-01

+KETA = -3.85E-03 A1 = 4.20E-03 A2 = 1.00E+00

+RDSW = 8.18E+02 PRWG = 2.35E-02 PRWB = -8.12E-02

+RDSW = 4000 PRWG = -9.54E-02 PRWB = -1.92E-03

+WR = 9.98E-01 WINT = 1.55E-07 LINT = 4.51E-10

+WR = 1 WINT = 1.47E-07 LINT = 1.04E-10

+DWG = -4.27E-09

+DWG = -1.09E-08

+DWB = 4.07E-09 VOFF = -4.14E-02 NFACTOR = 1.61E+00

+DWB = 1.14E-08 VOFF = -1.29E-01 NFACTOR = 2.01E+00

+CIT = 0 CDSC = 2.39E-04 CDSCD = 0.00E+00

+CIT = 0 CDSC = 2.40E-04 CDSCD = 0

+CDSCB = 0 ETA0 = 1 ETAB = -1.99E-01

+CDSCB = 0 ETA0 = 4.07E-02 ETAB = 6.84E-03

+DSUB = 1 PCLM = 1.32E+00 PDIBLC1 = 2.42E-04

+DSUB = 3.21E-01 PCLM = 5.96E+00 PDIBLC1 = 2.89E-03

+PDIBLC2 = 8.27E-03 PDIBLCB = -9.99E-04 DROUT = 9.72E-04

+PDIBLC2 = -1.45E-06 PDIBLCB = -1E-03 DROUT = 9.93E-04

+PSCBE1 = 7.24E+08 PSCBE2 = 9.96E-04 PVAG = 1.00E-02

+PSCBE1 = 7.88E+10 PSCBE2 = 5E-10 PVAG = 15

+DELTA = 1.01E-02 RSH = 3.33E+00 MOBMOD = 1

+DELTA = 9.96E-03 RSH = 2.6 MOBMOD = 1

+PRT = 0 UTE = -1.5 KT1 = -1.11E-01

+PRT = 0 UTE = -1.5 KT1 = -1.09E-01

+KT1L = 0 KT2 = 2.22E-02 UA1 = 4.34E-09

+KT1L = 0 KT2 = 2.19E-02 UA1 = 4.34E-09

+UB1 = -7.56E-18 UC1 = -5.62E-11 AT = 3.31E+04

+UB1 = -7.62E-18 UC1 = -5.63E-11 AT = 3.28E+04

+WL = 0 WLN = 9.95E-01 WW = 0

+WL = 0 WLN = 1 WW = 0

+WWN = 1.00E+00 WWL = 0 LL = 0

+WWN = 1.00E+00 WWL = 0 LL = 0

+LLN = 1 LW = 0 LWN = 1

+LLN = 1 LW = 0 LWN = 1

+LWL = 0 CAPMOD = 2 XPART = 0.5

+LWL = 0 CAPMOD = 2.01E+00 XPART = 0.5

+CGDO = 2.76E-10 CGSO = 2.76E-10 CGBO = 1.00E-12

+CGDO = 2.10E-10 CGSO = 2.12E-10 CGBO = 1.00E-12

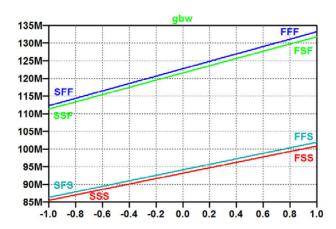

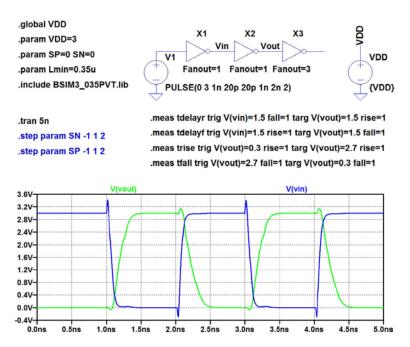

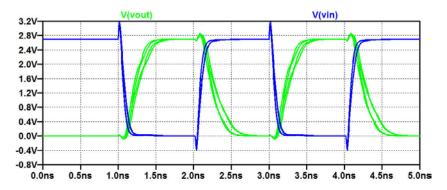

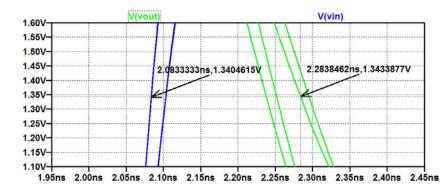

+CJ = 9e-4 PB = 7.95E-01 MJ = 3.53E-01