# **DIGITAL ELECTRONICS**

Ashish Murolia R. K. Kanodia

JHUNJHUNUWALA

Digital Electronics 1e Ashish Murolia and RK Kanodia

Copyright O By JHUNJHUNUWALA

Information contained in this book has been obtained by author, from sources believes to be reliable. However, neither Jhunjhunuwala nor its author guarantee the accuracy or completeness of any information herein, and Jhunjhunuwala nor its author shall be responsible for any error, omissions, or damages arising out of use of this information. This book is published with the understanding that Jhunjhunuwala and its author are supplying information but are not attempting to render engineering or other professional services.

MRP 420.00

# JHUNJHUNUWALA

B-48, Dhanshree Tower Ist, Central Spine, Vidhadhar Nagar, Jaipur – 302035 Ph : +91 – 40 – 64582577 www.jhunjhunuwala.com email : info@jhunjhunuwala.com

Printed by Nodia and Company, 302013

# PREFACE

This book provides a whole coverage of the course of Digital Electronics for Engineering graduates of various Universities across the country. The topics presented in this book are discussed using a simplified approach that greatly enhances learning. The book contains eleven chapters and each chapter is organized in a step-by-step progression of concepts and theory. The text is written in a simple language with an emphasis of clarity of the topics. A large number of solved examples have been included in theory as well as end of each chapter. The key features of the books are summarized as follows:

Key Features:

- Standardized Chapter Organization

- Succinct and Well-explained Theory

- $\ensuremath{\mathscr{P}}$  Reader Notes, Do Remember and Confusion Clearing points in the side column

- Illustrative Diagrams

- Problem Solving Methodology

- Æ Examples associated with Problem Solving Methodology

- $\checkmark$  More than 550 Solved Examples at the End of Chapter

- $\ensuremath{\mathscr{P}}$  Review Question and Problems

The author would like to thank editorial and production team of JHUNJHUNUWALA for providing professional support for this project through all phases of its development. Finally, we want to express our appreciation to our family for their support and motivation.

Although we have put a vigorous effort in preparing this book, some errors may have crept in. We shall appreciate and greatly acknowledge the comments, criticism and suggestion from the users of this book which leads to some improvement.

Authors

# CONTENTS

# 1 NUMBER SYSTEMS

| 1.1  | Introduction 1                               |

|------|----------------------------------------------|

| 1.2  | Analog and Digital Systems 1                 |

| 1.3  | Number Systems 3                             |

| 1.4  | Number System Conversion 6                   |

| 1.5  | Summary of Number Conversion 15              |

| 1.6  | Basic Binary Arithmetic 19                   |

| 1.7  | Complements of Numbers 23                    |

| 1.8  | Number Representation in Binary 29           |

| 1.9  | Complement Binary Arithmetic 32              |

| 1.10 | Arithmetic Overflow 44                       |

| 1.11 | Hexadecimal Arithmetic 45                    |

| 1.12 | Octal Arithmetic 50                          |

| 1.13 | Decimal Arithmetic 55                        |

| 1.14 | Floating Point Numbers 60                    |

| 1.15 | Floating Point Arithmetic 64                 |

|      | Review Questions and Problems 78             |

| BINA | RY CODES                                     |

| 2.1  | Introduction 79                              |

| 2.2  | Classification of Codes 79                   |

| 2.3  | Binary Coded Decimal (BCD) Code or 8421 Code |

- 2.4 BCD Arithmetic 83

- 2.5 The Excess 3 Code 91

- 2.6 Gray Code 93

2.

- 2.7 2-4-2-1 Code 98

- 2.8 Biquinary Code 100

- 2.9 5-Bit BCD Codes 100

- 2.10 Alphanumeric Codes 101

- 2.11 Error Detecting Codes 103

- 2.12 Error-Correcting Code 104

81

Review Questions and Problems 110

# 3 BOOLEAN ALGEBRA AND LOGIC GATES

- 3.1 Introduction 111

- 3.2 Boolean Algebra 111

- 3.3 Truth Table 112

- 3.4 Basic Boolean Operations 112

- 3.5 Comparison Between Boolean Algebra and Ordinary Algebra 114

- 3.6 Postulates and Theorems of Boolean Algebra 114

- 3.7 Equivalent and Complement of Boolean Expressions 124

- 3.8 Principal of Duality 125

- 3.9 Simplification of Boolean Expressions Using Boolean Algebra 127

- 3.10 Logic Gates 132

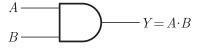

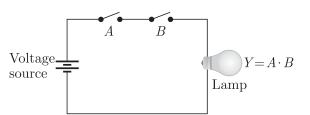

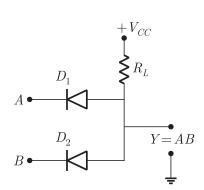

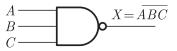

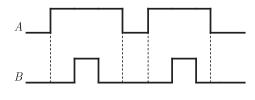

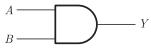

- 3.11 the AND Gate 133

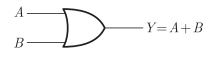

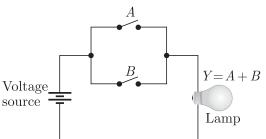

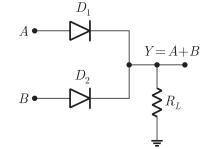

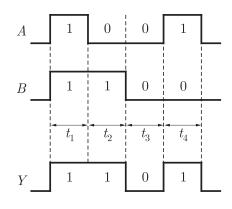

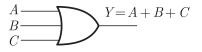

- 3.12 The OR Gate 135

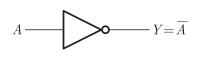

- 3.13 The NOT Gate 137

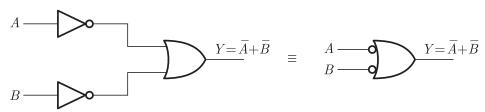

- 3.14 The NAND Gate 138

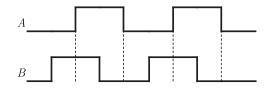

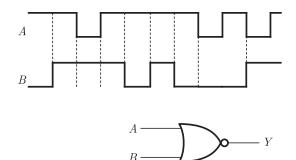

- 3.15 The NOR Gate 140

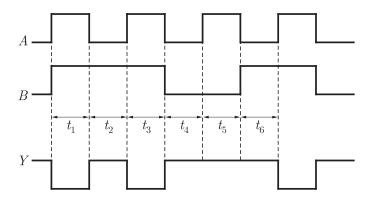

- 3.16 The Exclusive-OR (XOR) Gate 142

- 3.17 The Exclusive-NOR (XNOR) Gate 143

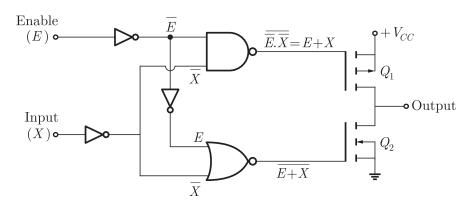

- 3.18 Inhibit Gate 144

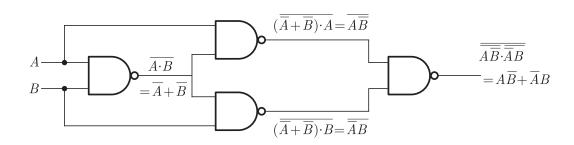

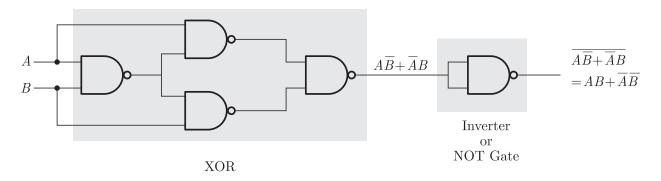

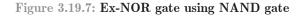

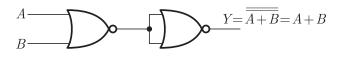

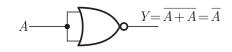

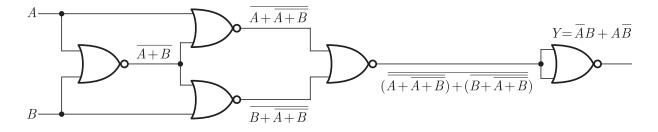

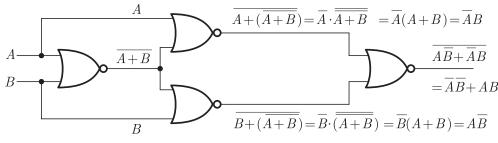

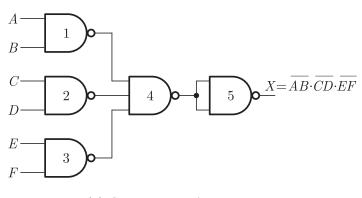

- 3.19 Universal Gate 146

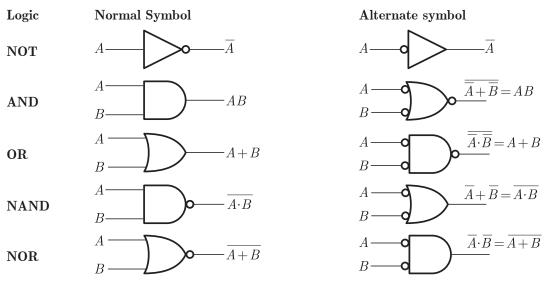

- 3.20 Alternate Logic-Gate Representations 151

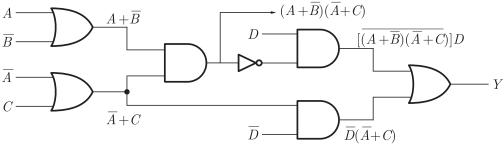

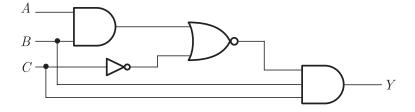

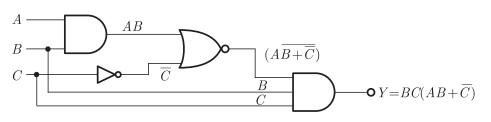

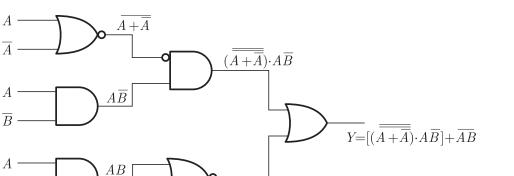

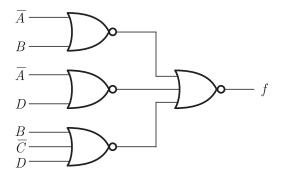

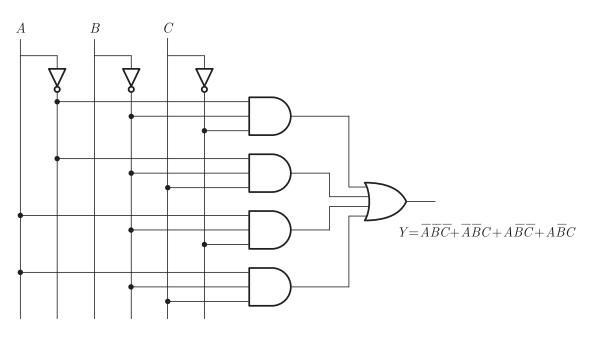

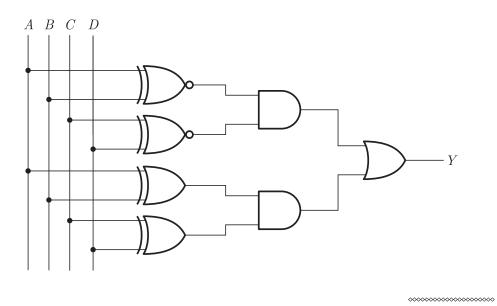

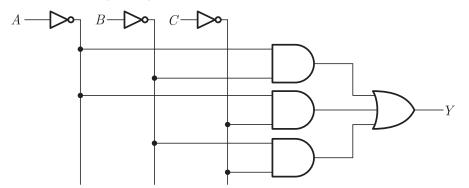

- 3.21 Boolean Analysis of Logic circuits 153

- 3.22 Converting Logic Diagrams to NAND/NOR Logic 159 Review Questions and Problems 184

# 4 MINIMIZATION TECHNIQUES

- 4.1 Introduction 186

- 4.2 Representation for Boolean Functions 186

- 4.3 Converting Expressions to Standard SOP or POS Forms 191

- 4.4 Converting Standard SOP Form to Standard POS Form 196

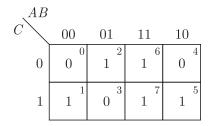

- 4.5 Boolean Expressions and Truth Tables 199

- 4.6 Calculation of Total Gate Inputs using SOP and POS Forms 202

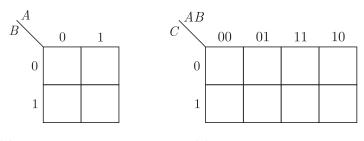

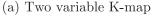

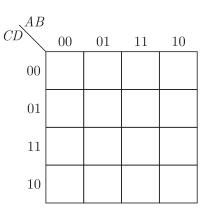

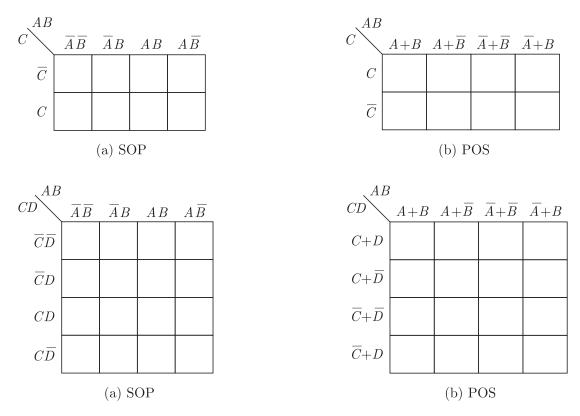

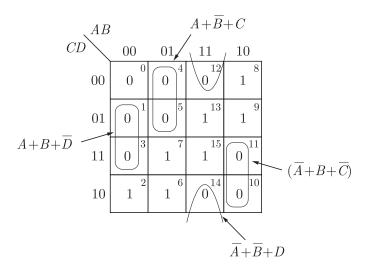

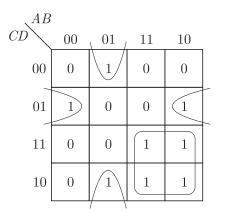

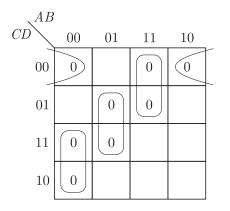

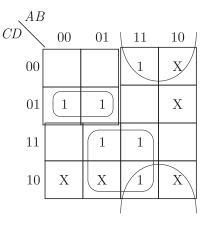

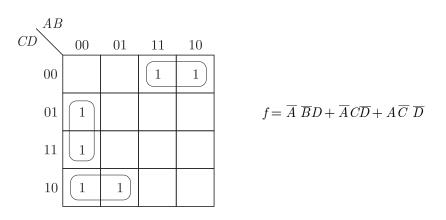

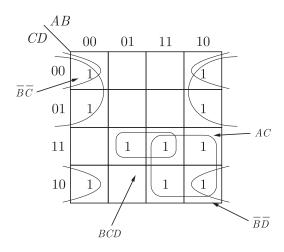

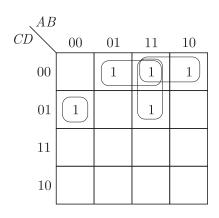

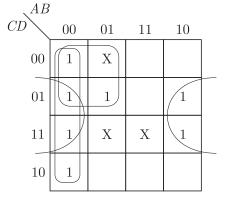

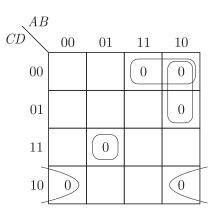

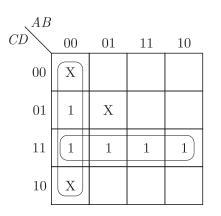

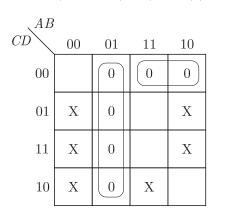

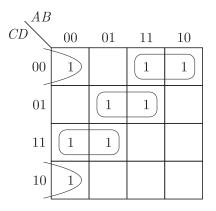

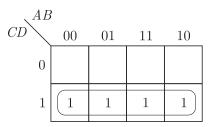

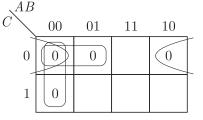

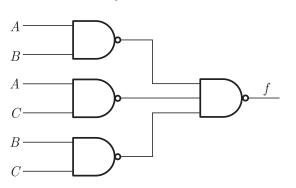

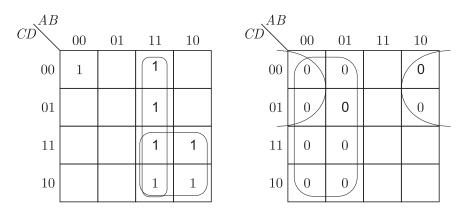

- 4.7 Karnaugh Map (K-map) 203

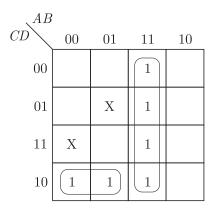

- 4.8 Don't Care Conditions 232

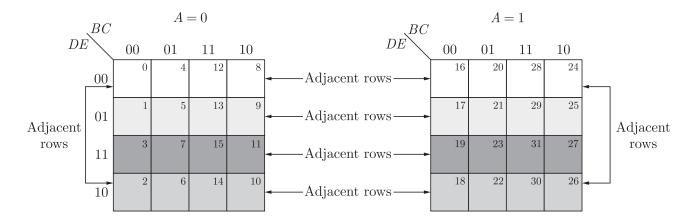

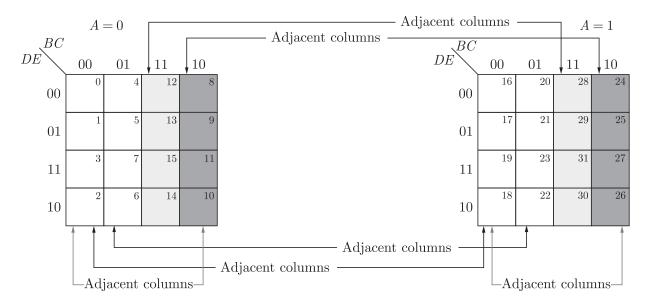

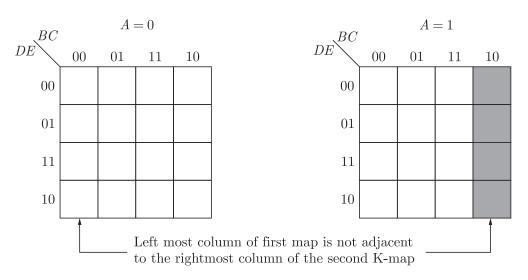

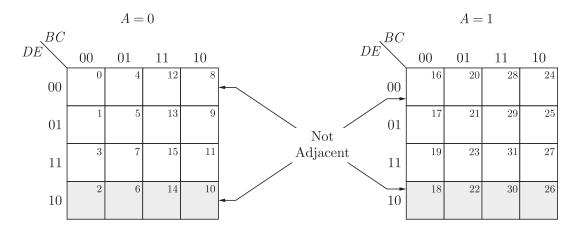

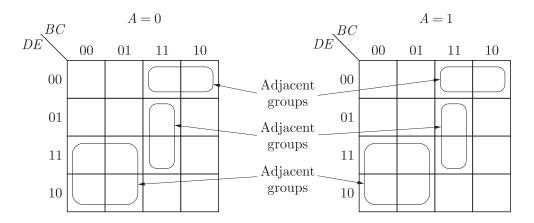

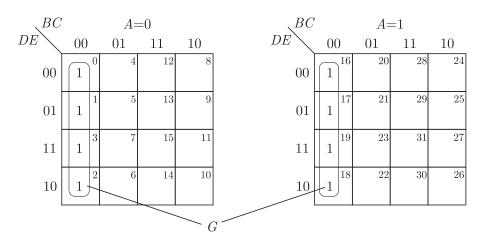

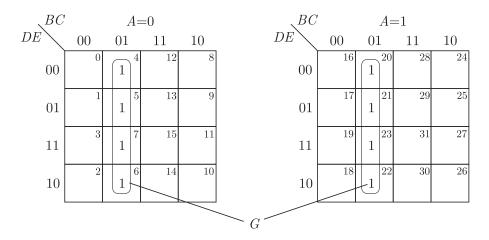

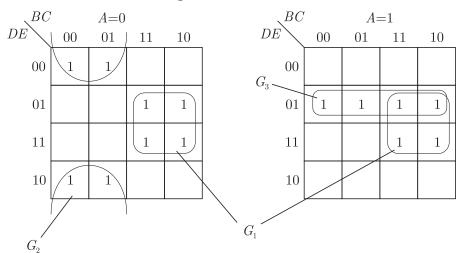

- 4.9 Five Variable K-map 237

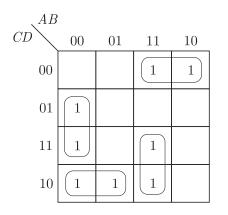

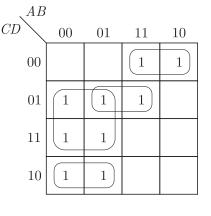

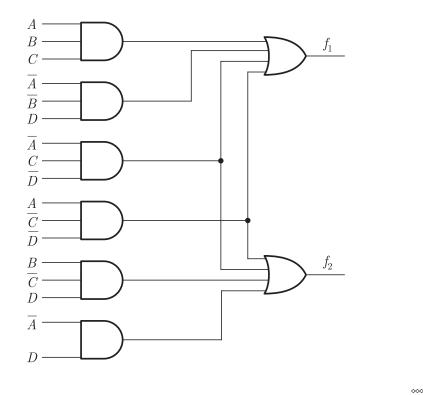

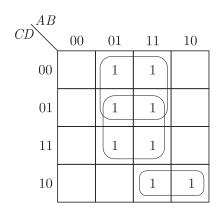

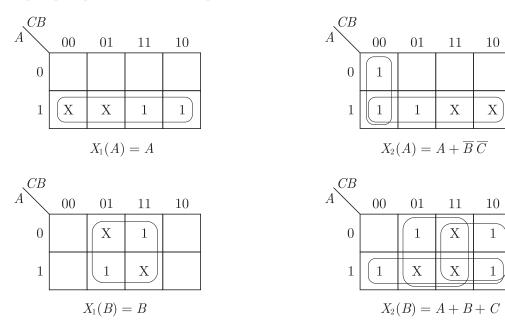

- 4.10 K-maps For Multi-Output Functions 241

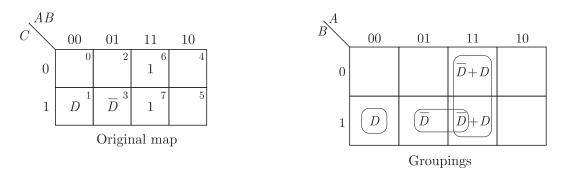

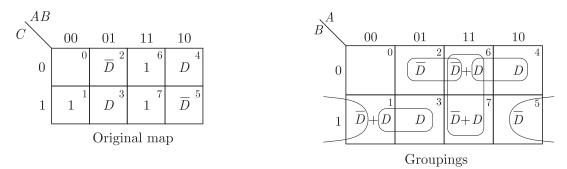

- 4.11 Variable Mapping 243

- 4.12 Limitations of K-map 245

- 4.13 Quine McCluskey or Tabular Method of Minimization of Logic Functions 245 Review Questions and Problems 287

# 5 COMBINATIONAL ARITHMETIC CIRCUITS

- 5.1 Introduction 290

- 5.2 Design Procedure For Combination Logic Circuits 290

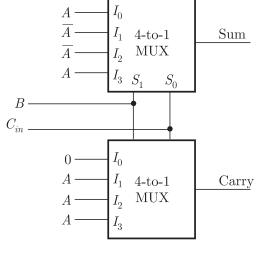

- 5.3 Arithmetic Circuits 292

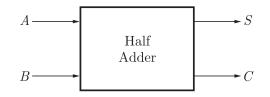

- 5.4 Adders 293

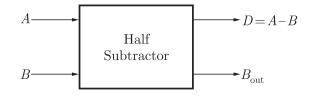

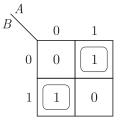

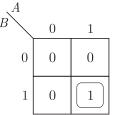

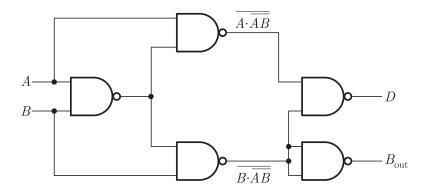

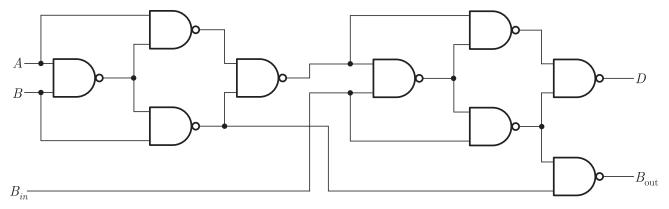

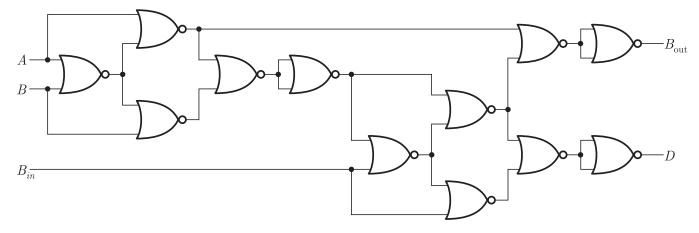

- 5.5 Subtractors 300

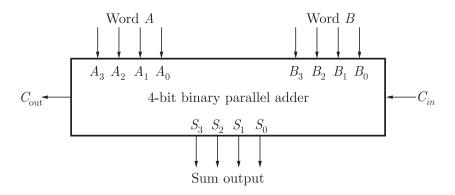

- 5.6 Binary Parallel Adder 307

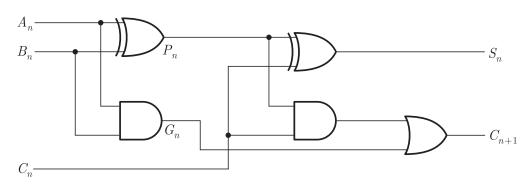

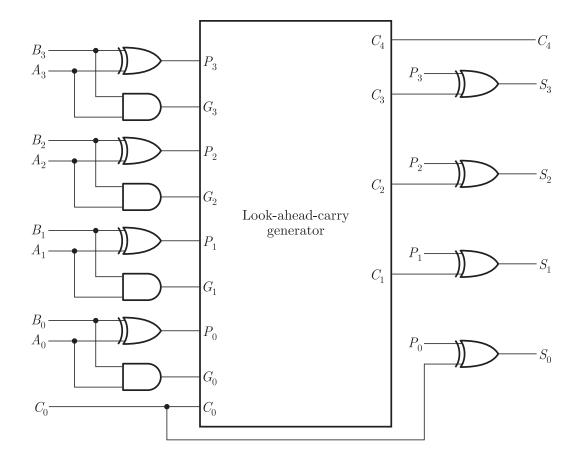

- 5.7 Carry Look-Ahead Adder 308

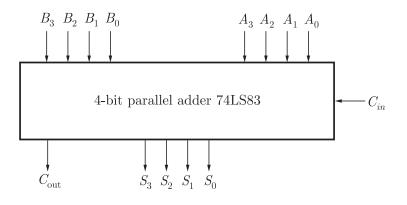

- 5.8 IC Parallel Adders 312

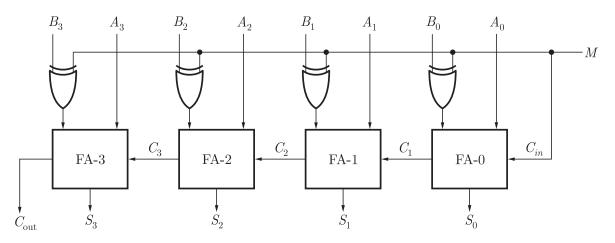

- 5.9 Parallel Subtractor 313

- 5.10 Parallel Adder/Subtractor 313

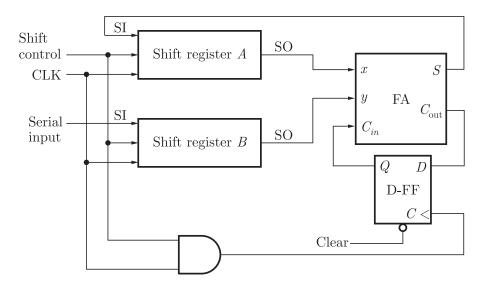

- 5.11 Serial Adder 314

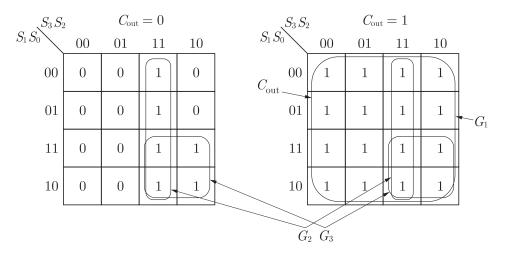

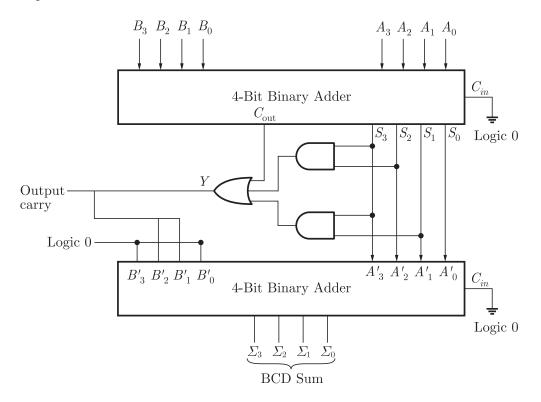

- 5.12 BCD Adder **316**

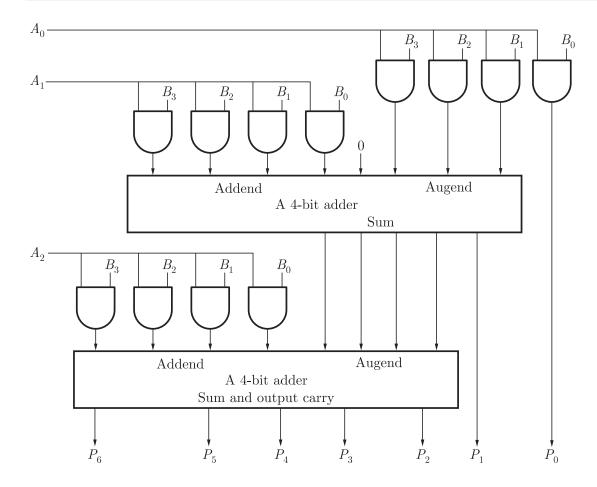

- 5.13 Binary Multipliers 318

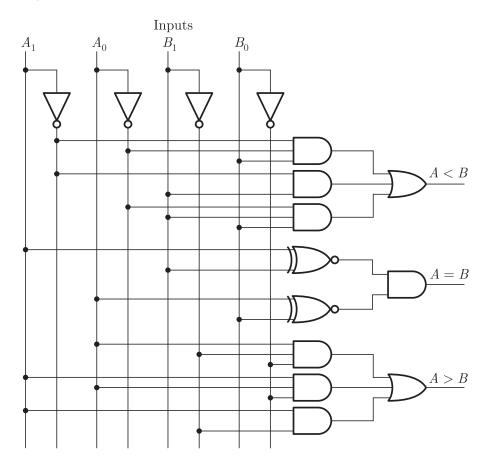

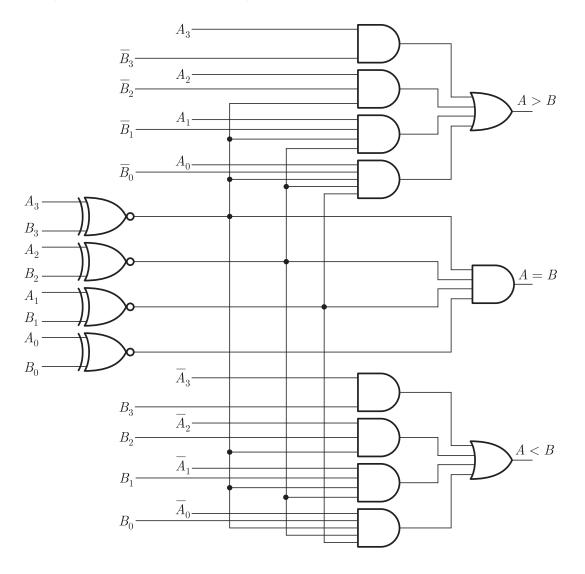

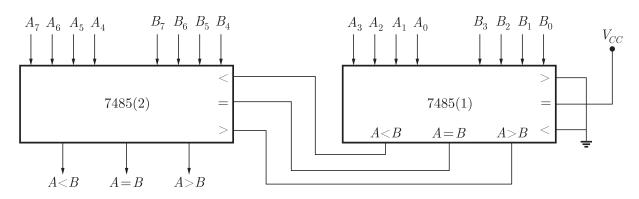

- 5.14 Magnitude Comparator 320 Review Questions and Problems 330

# 6 COMBINATIONAL LOGIC CIRCUITS

- 6.1 Introduction 332

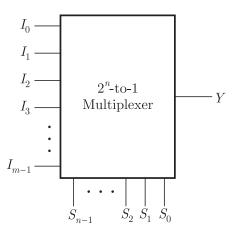

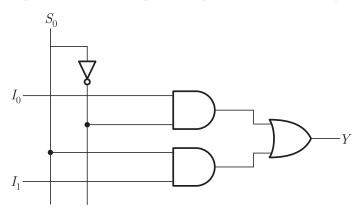

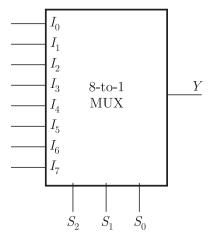

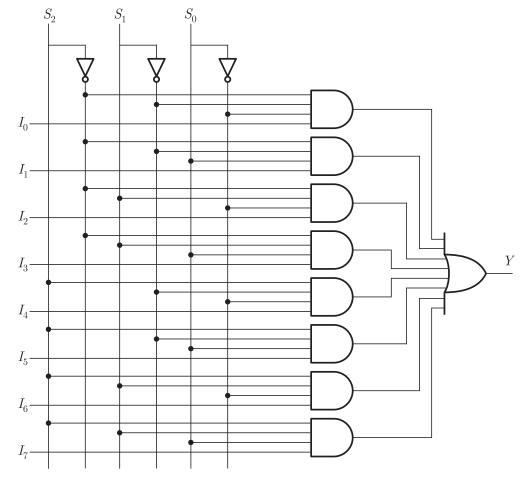

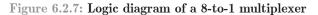

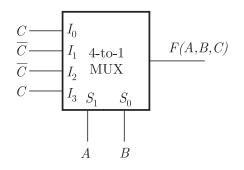

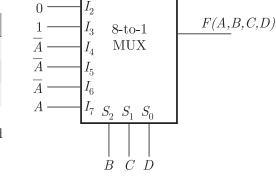

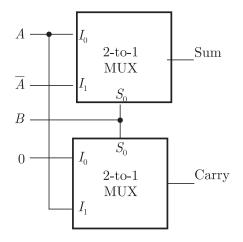

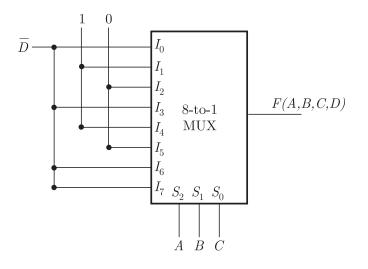

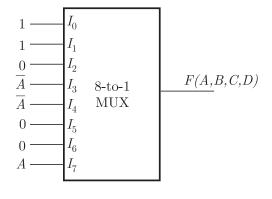

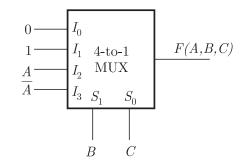

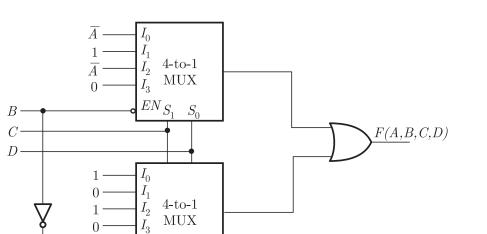

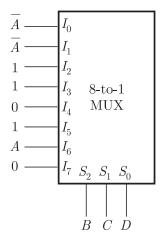

- 6.2 Multiplexer 332

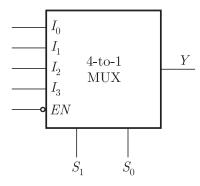

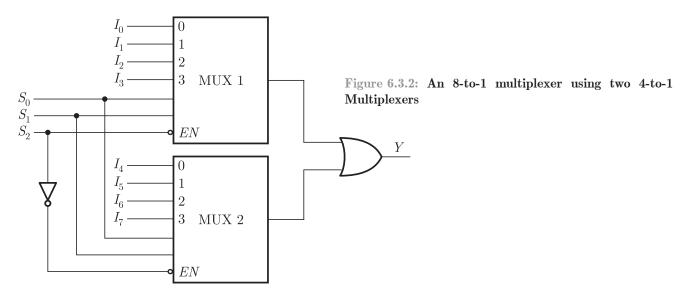

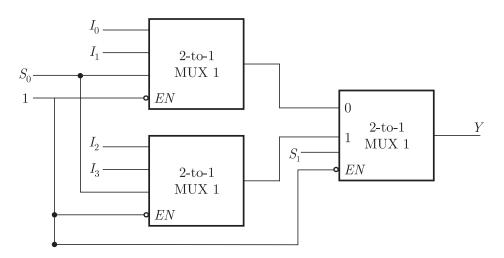

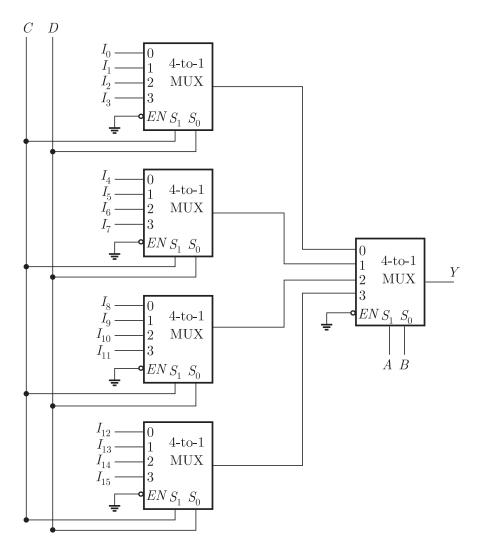

- 6.3 Implementation of Higher order multiplexers using Lower order multiplexers 337

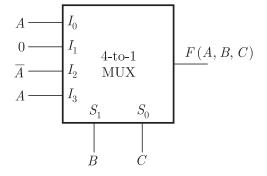

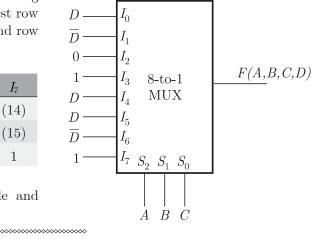

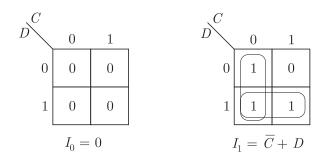

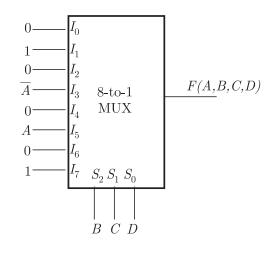

- 6.4 Implementation of Boolean Expressions using Multiplexers 341

- 6.5 Applications of Multiplexers 349

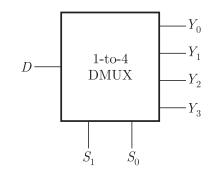

- 6.6 Demultiplexer 349

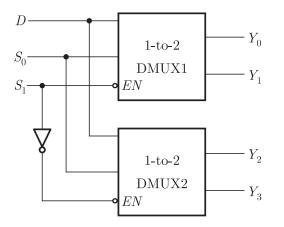

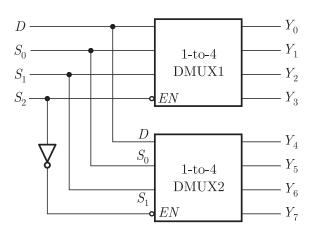

- 6.7 Implementation of Higher order Demultiplexers using Lower order Demultiplexers 352

- 6.8 Applications of Demultiplexers 354

- 6.9 Comparison Between Multiplexer and Demultiplexer 354

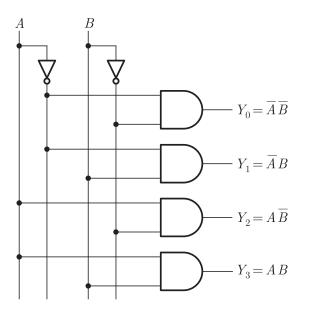

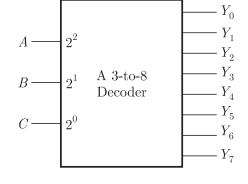

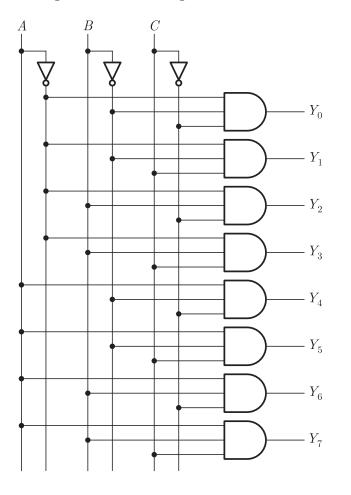

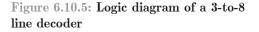

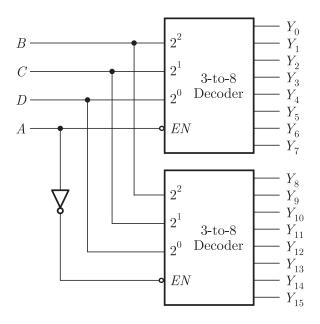

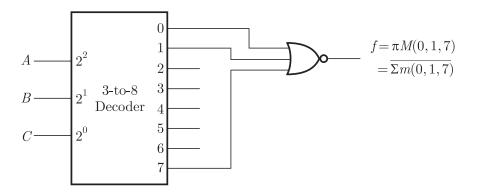

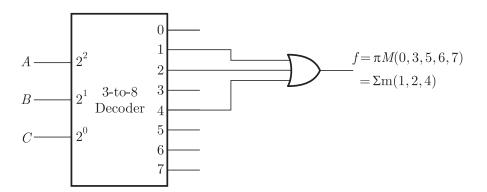

- 6.10 Decoder 355

- 6.11 Implementation of Higher Order Decoders using Lower Order Decoders 358

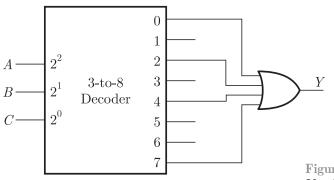

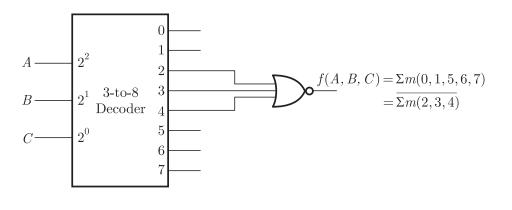

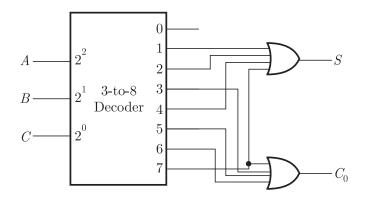

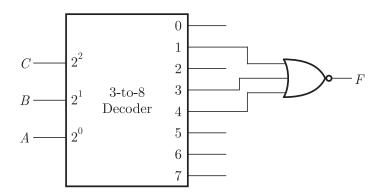

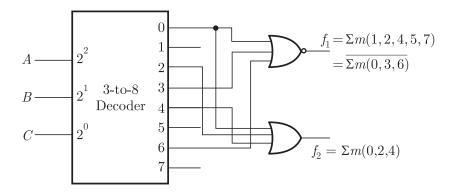

- 6.12 Implementation of Logic Expressions using Decoders 360

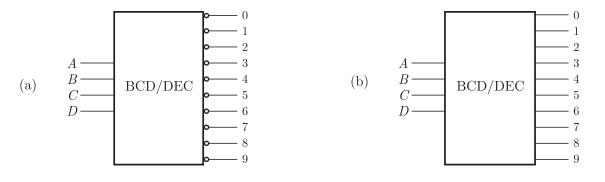

- 6.13 BCD-to-Decimal Decoder 363

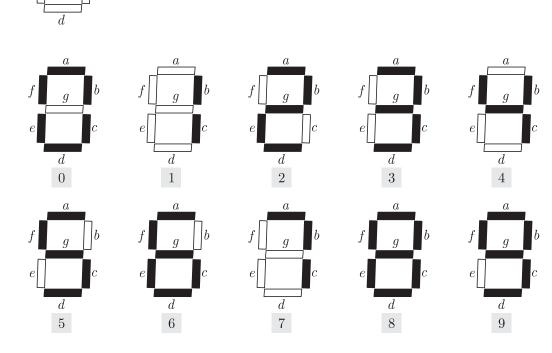

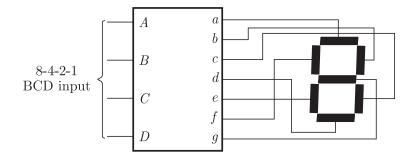

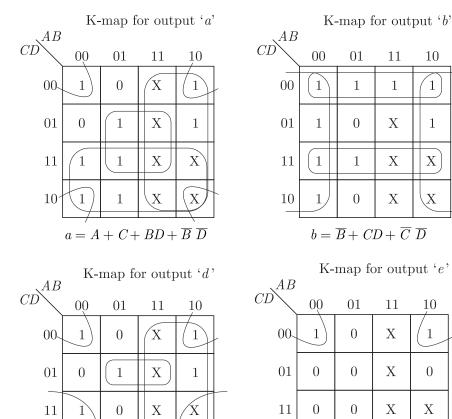

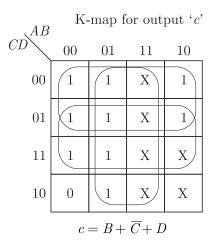

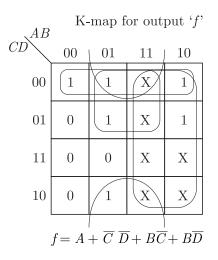

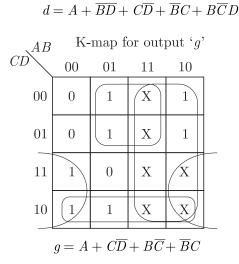

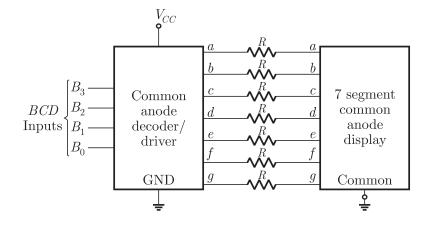

- 6.14 BCD-to-Seven Segment Decoder 365

- 6.15 Applications of Decoder 369

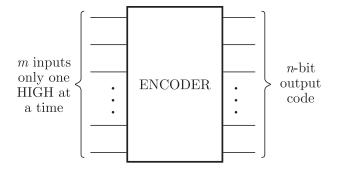

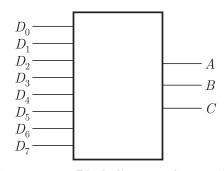

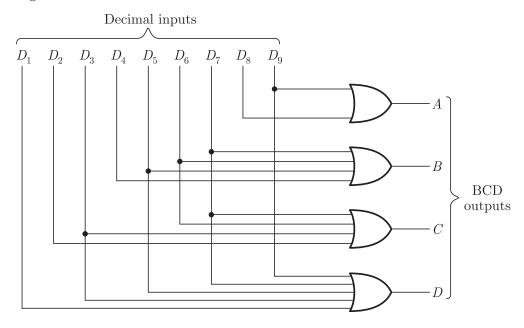

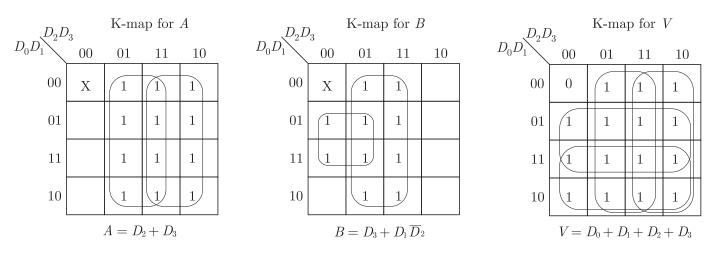

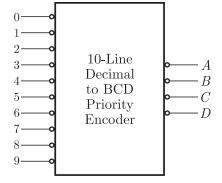

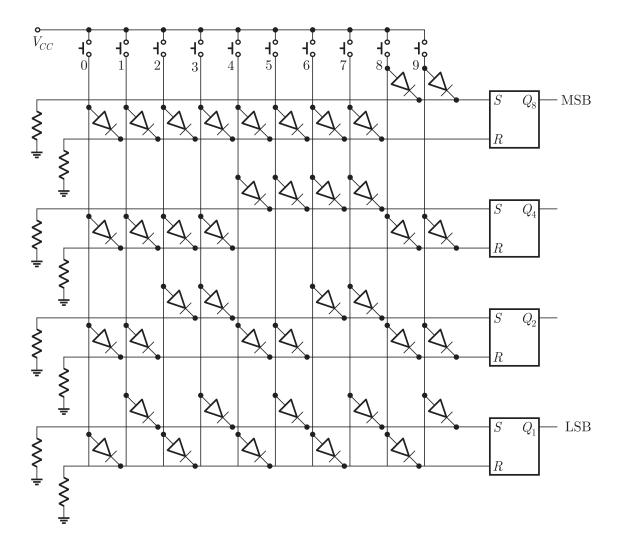

- 6.16 Encoders 369

- 6.17 Keyboard Encoders 376

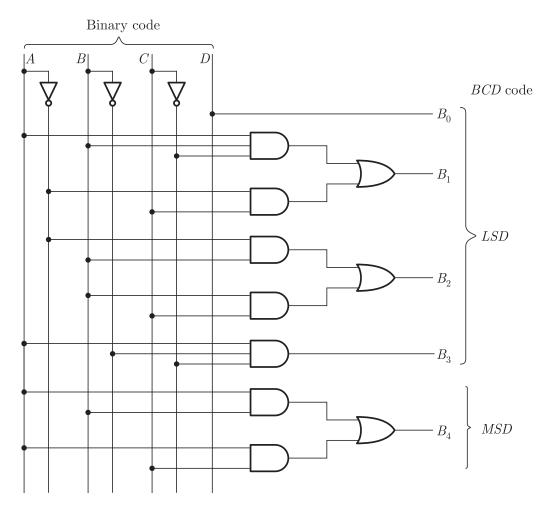

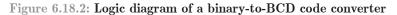

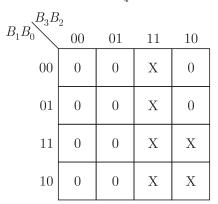

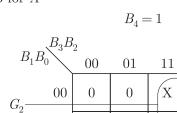

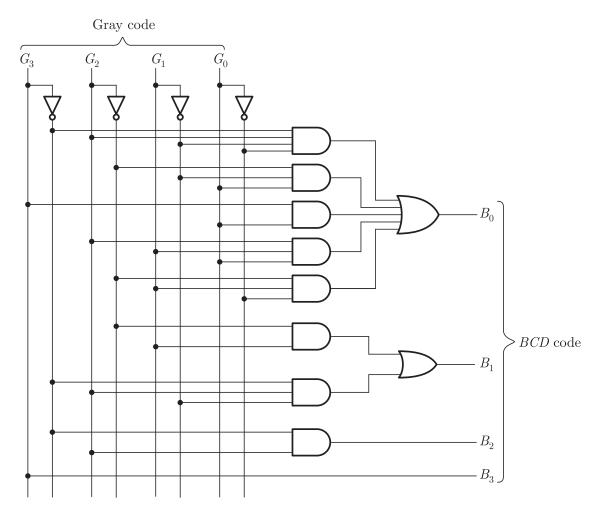

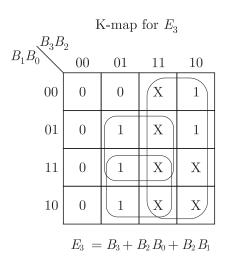

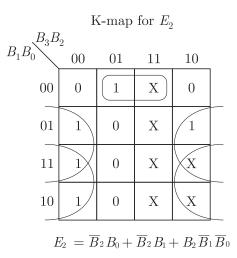

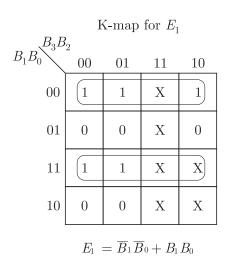

- 6.18 Code Converters 377

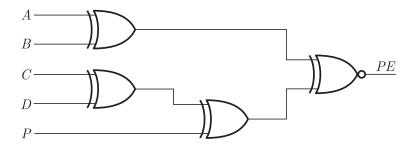

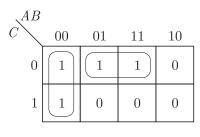

- 6.19 Parity Generator 393

- 6.20 Parity Checker 396

- 6.21 Hazards In Combinational Circuits 400 Review Questions and Problems 421

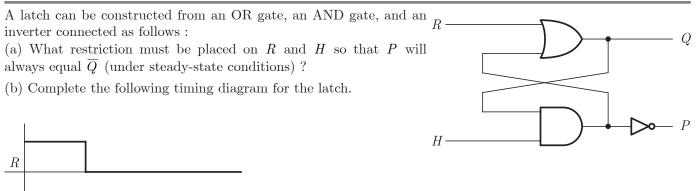

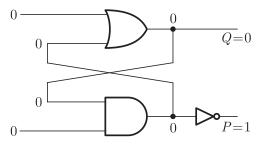

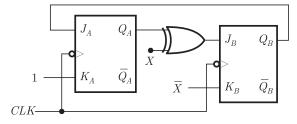

# 7 LATCHES AND FLIP-FLOPS

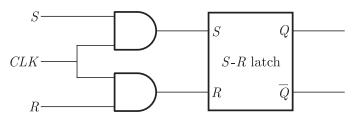

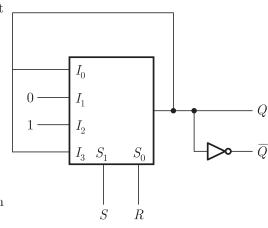

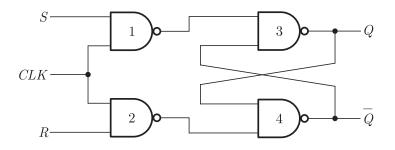

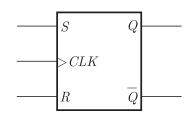

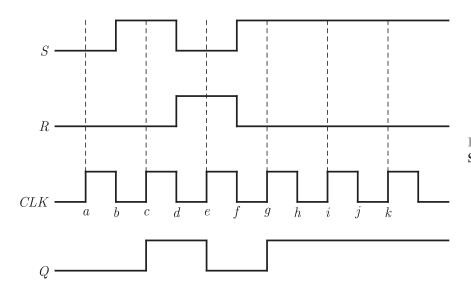

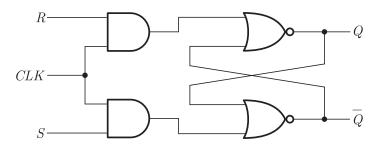

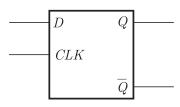

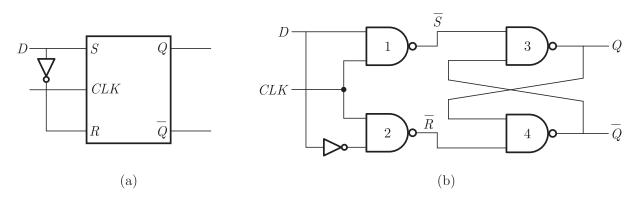

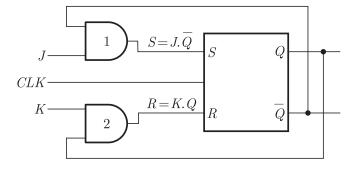

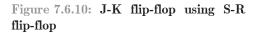

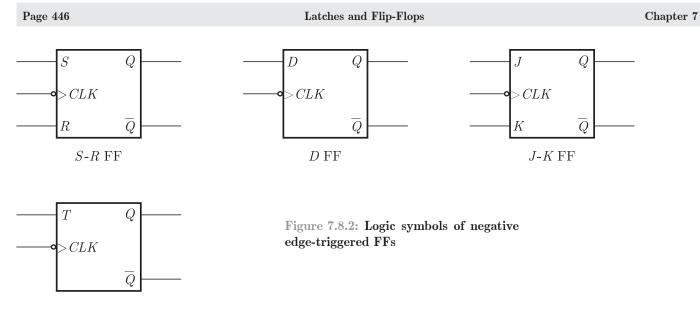

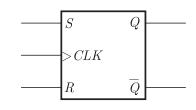

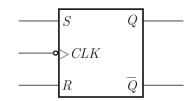

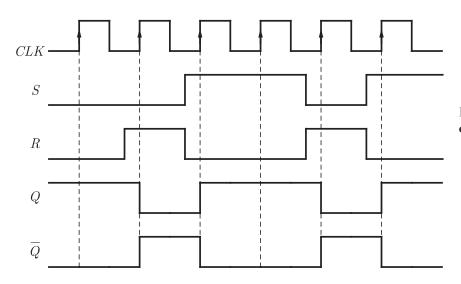

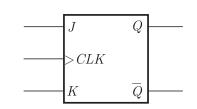

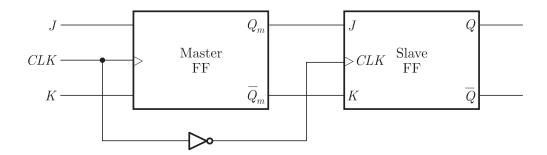

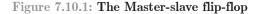

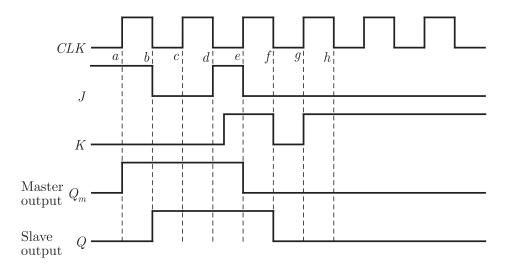

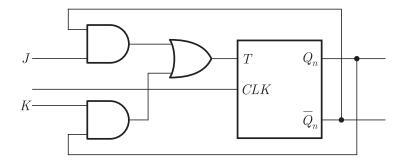

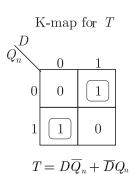

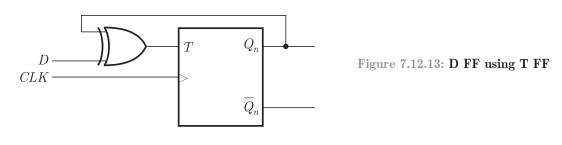

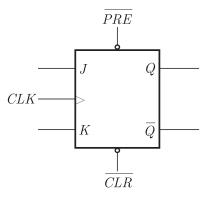

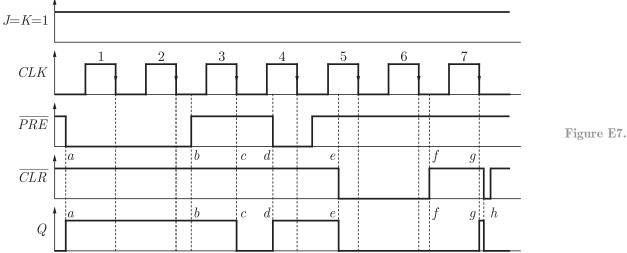

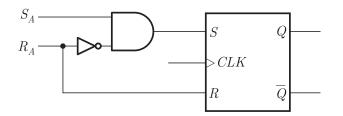

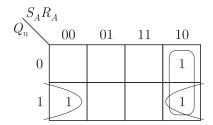

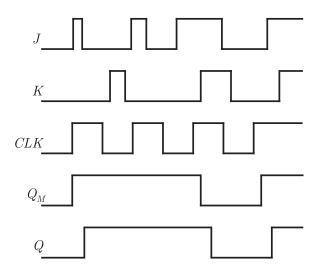

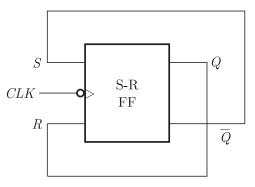

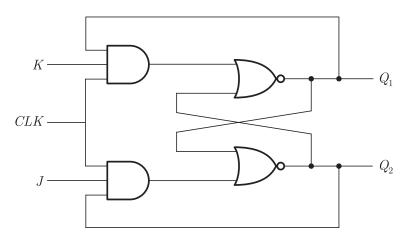

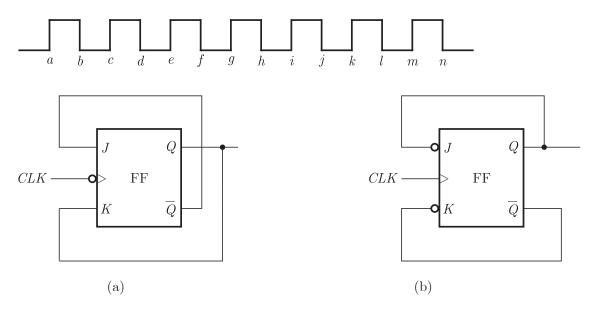

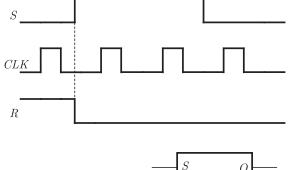

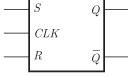

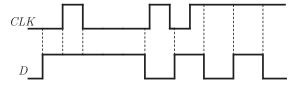

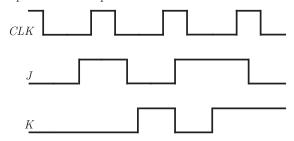

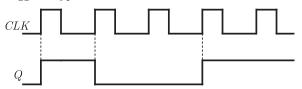

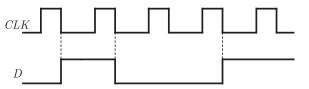

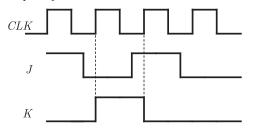

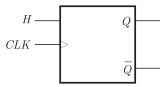

7.1Introduction 423 7.2**Classification of Digital Circuits** 423 7.3425**Classification of Sequential Circuits** 7.4Latches and Flip-Flops 425S-R Latch 7.5426 7.6 Flip-Flops 4347.7Triggering of Flip-Flops 443 7.8 Edge Triggered Flip-Flops 4457.9 Race Around Condition in J-K Flip Flop 4547.10Master-Slave J-K Flip Flop 455

- 7.11 Various Representations of Flip-Flops 457

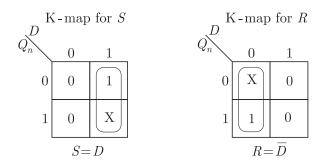

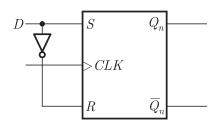

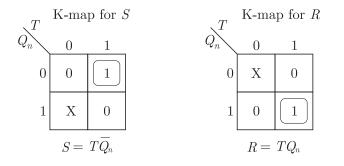

- 7.12 Conversion of Flip-Flops 461

- 7.13 Asynchronous Inputs in Flip-Flops 477

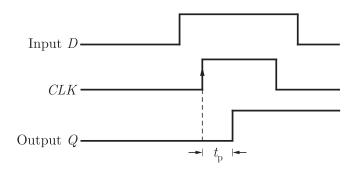

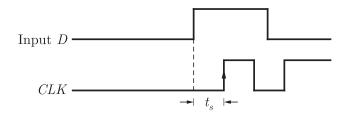

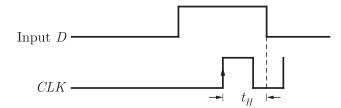

- 7.14 Operating Characteristic (Timing Parameters) of Flip-Flops 479

- 7.15 Application of Flip-FLops 481 Review Questions and Problems 497

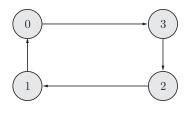

# 8. COUNTERS

- 8.1 Introduction 499

- 8.2 Classification of Counters 499

- 8.3 MOD Number or Modulus of a Counter 500

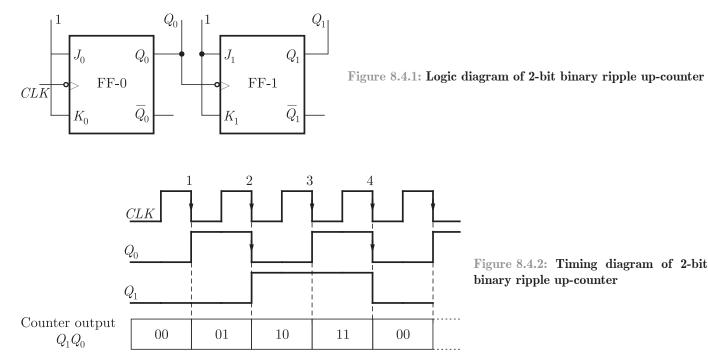

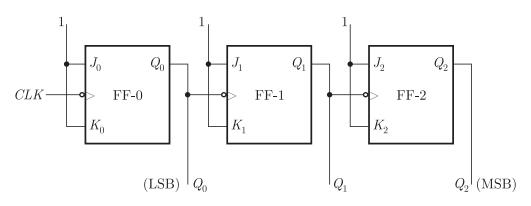

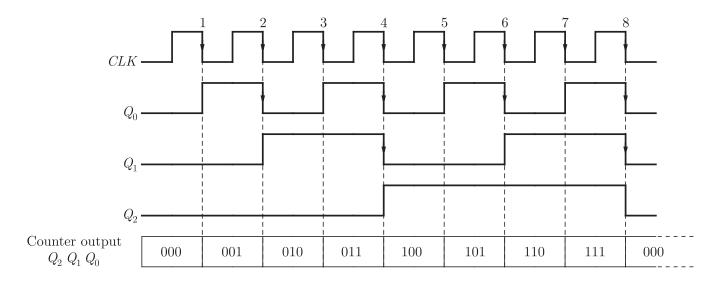

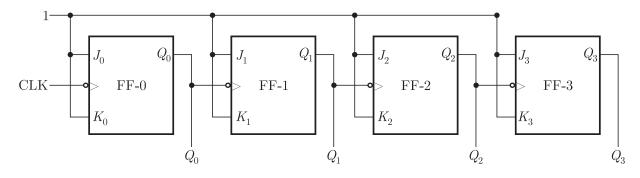

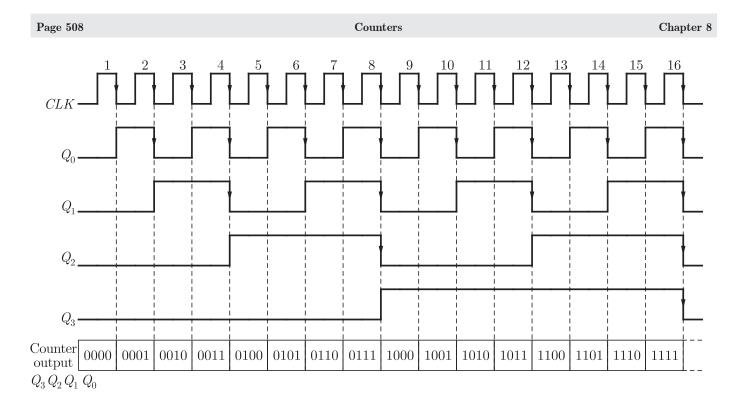

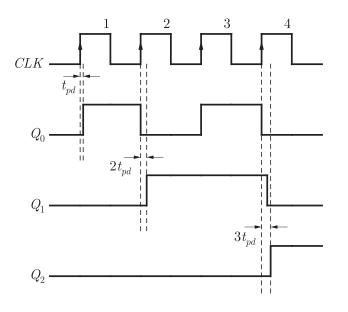

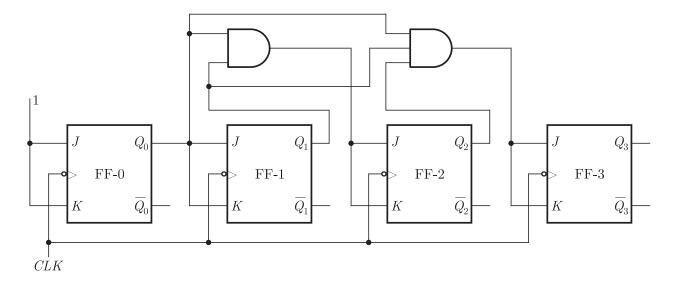

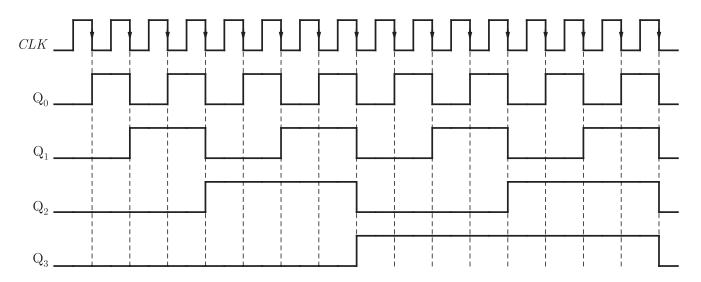

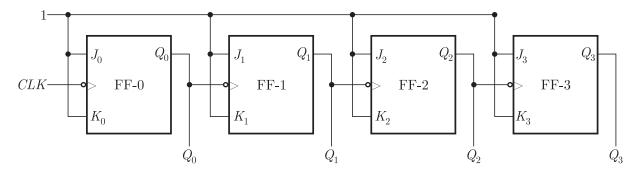

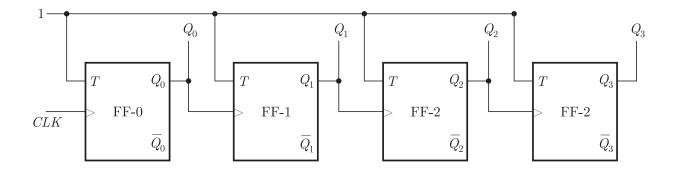

- 8.4 Asynchronous Counters or Binary Ripple Counters 501

- 8.5 Design of Ripple Counters 512

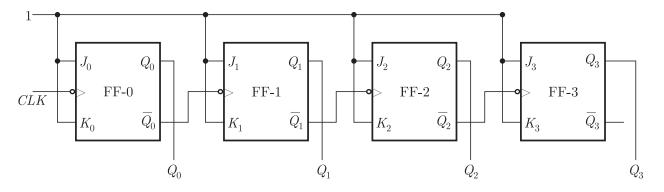

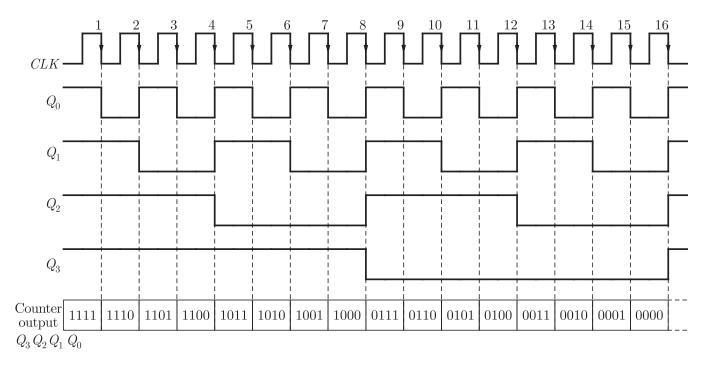

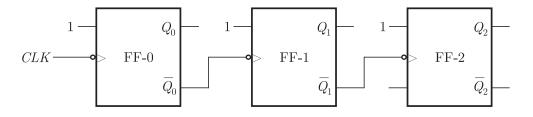

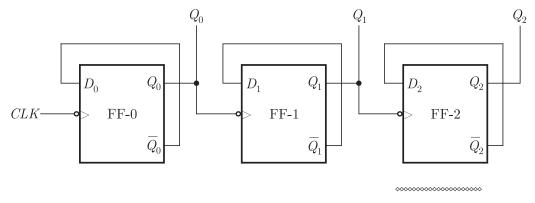

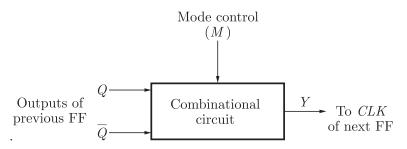

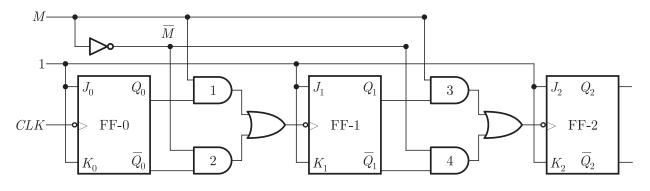

- 8.6 Up/Down Ripple Counters 514

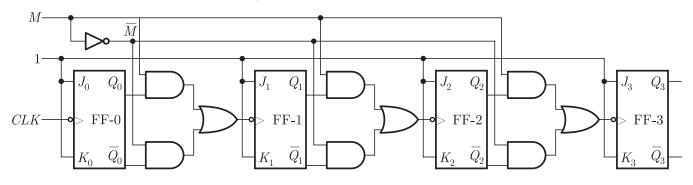

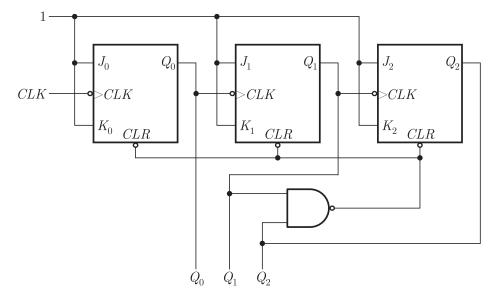

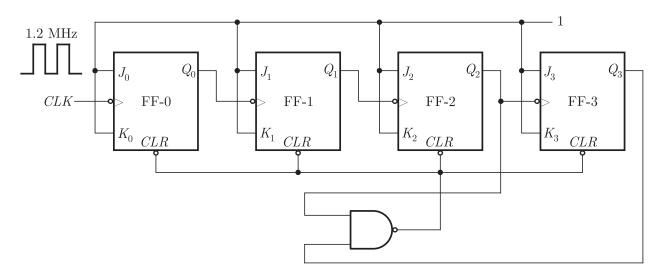

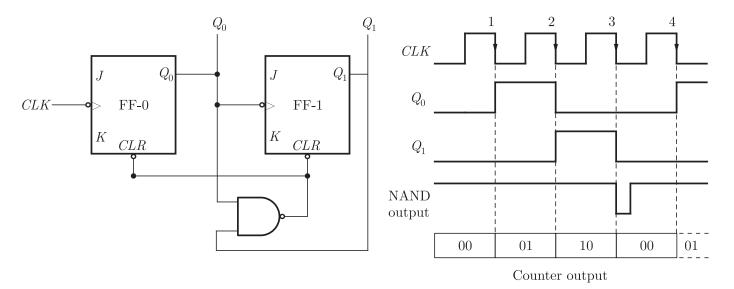

- 8.7 Binary Ripple Counter with a Modulus of less than  $2^n$  517

- 8.8 Propagation Delay In ripple Counters 523

- 8.9 Decoding a Ripple Counter 525

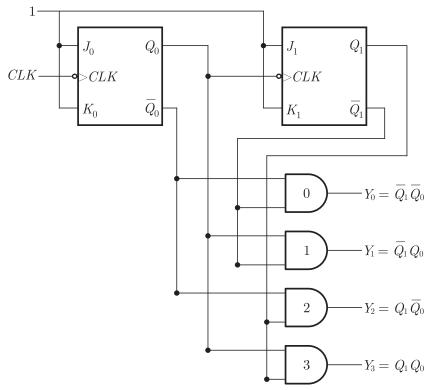

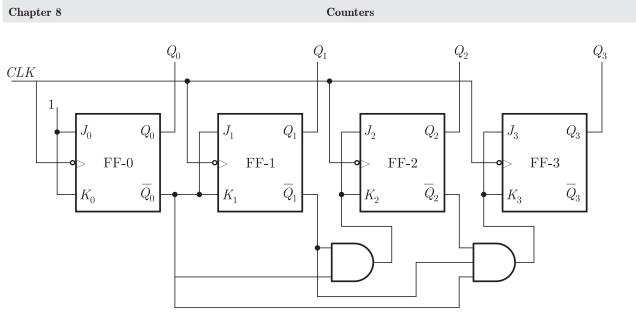

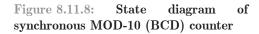

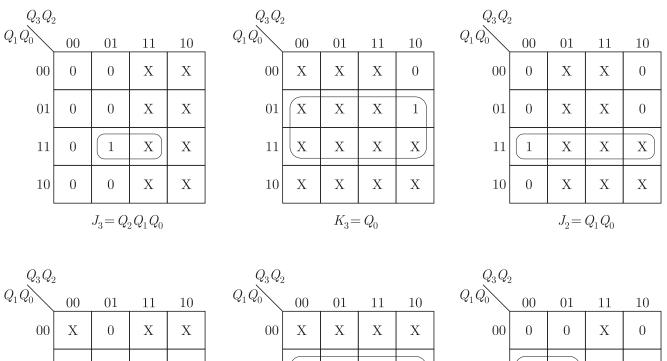

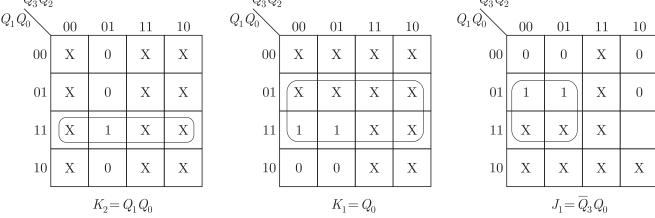

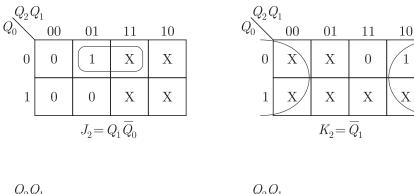

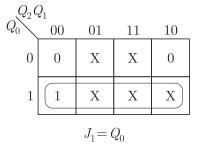

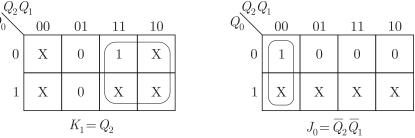

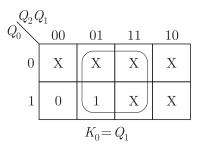

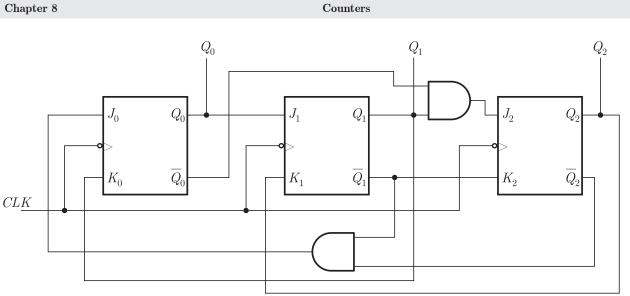

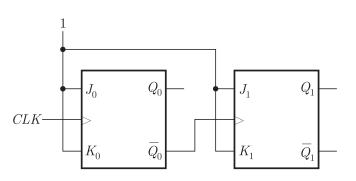

- 8.10 Synchronous Counter 528

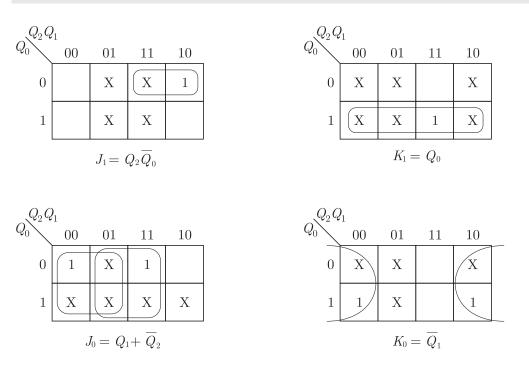

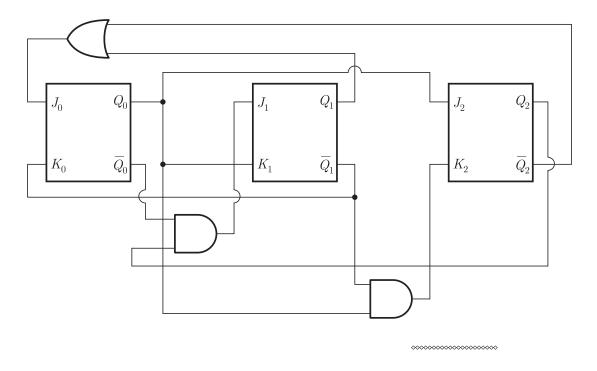

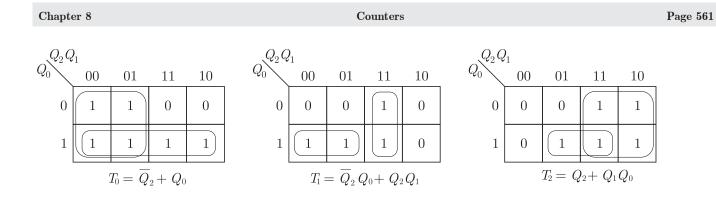

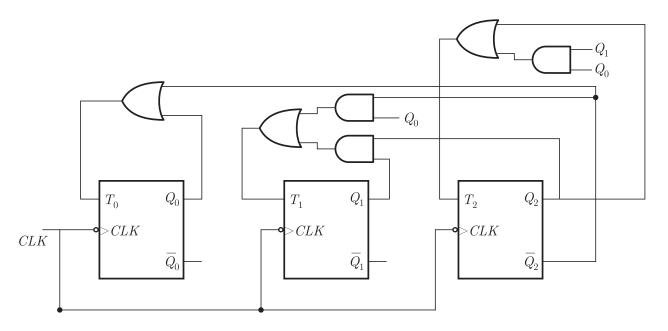

- 8.11 Design of Synchronous Counters 531

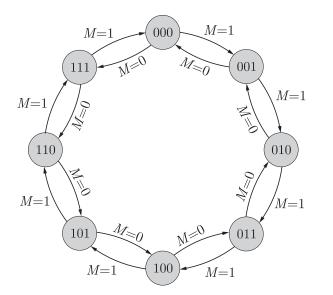

- 8.12 Synchronous Up/Down Counters 545

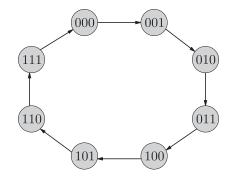

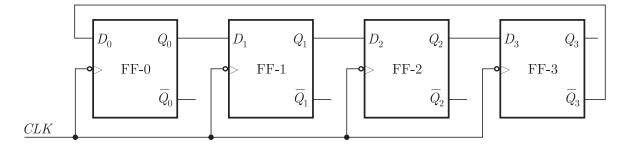

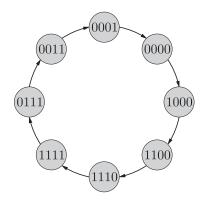

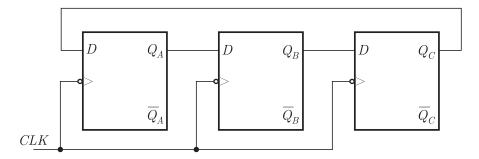

- 8.13 Shift Register Counters 548

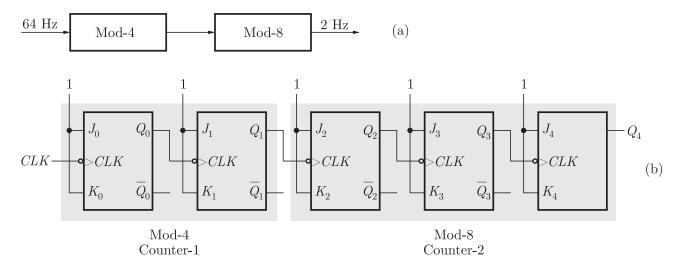

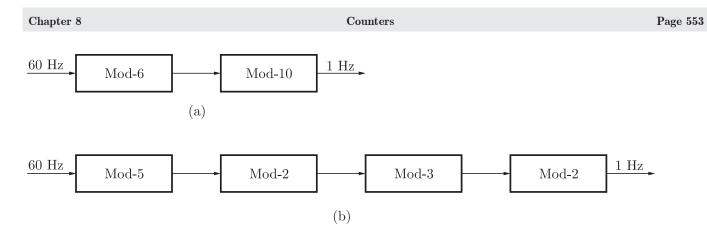

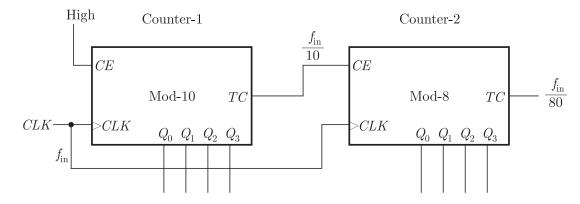

- 8.14 Cascading Counters 552

- 8.15 Applications of Counters 554 Review Questions and Problems 577

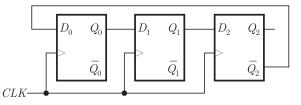

# 9 REGISTERS

- 9.1 Introduction 579

- 9.2 Buffer Register 579

- 9.3 Shift Register 580

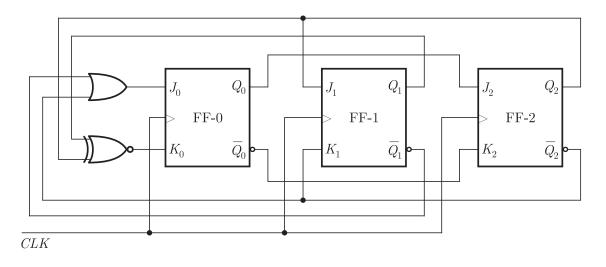

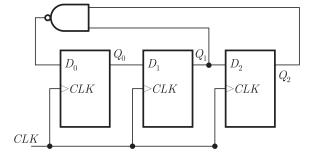

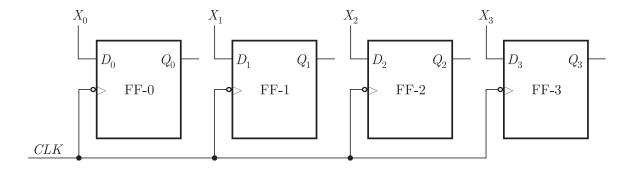

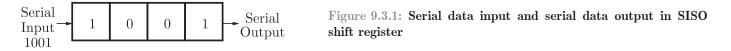

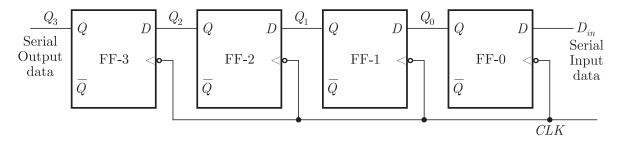

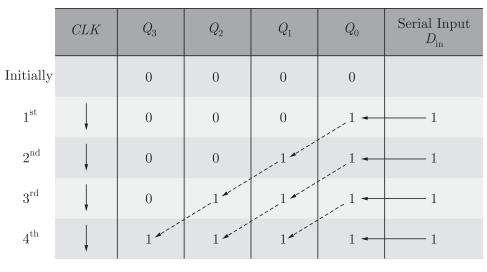

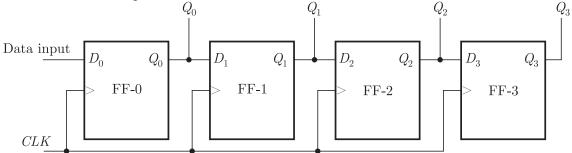

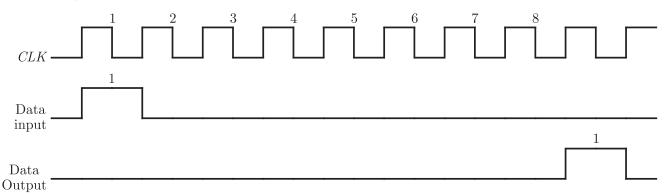

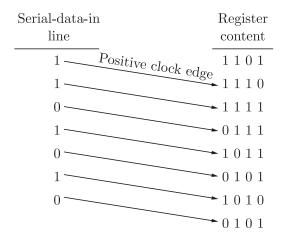

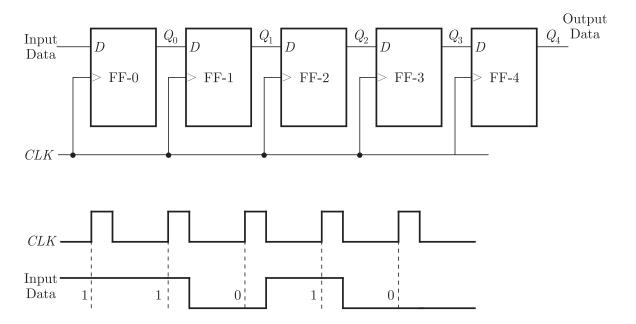

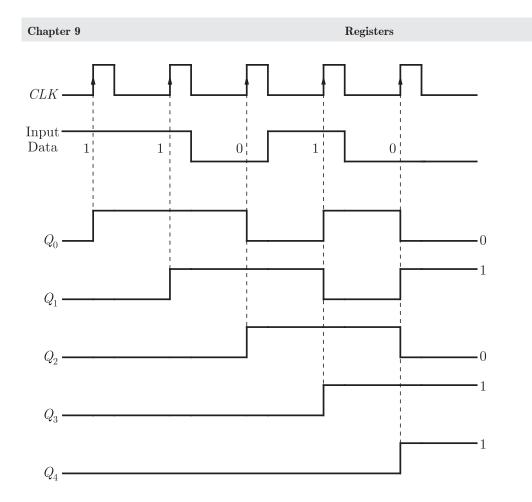

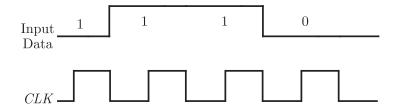

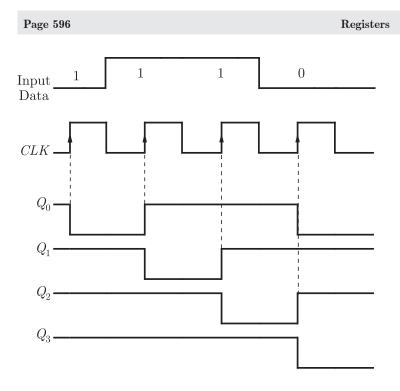

- 9.4 Serial-In Serial-Out Shift Register 581

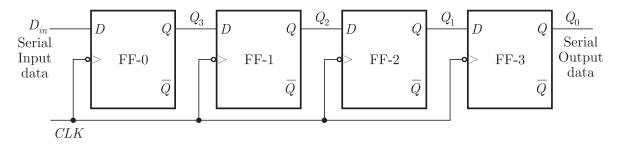

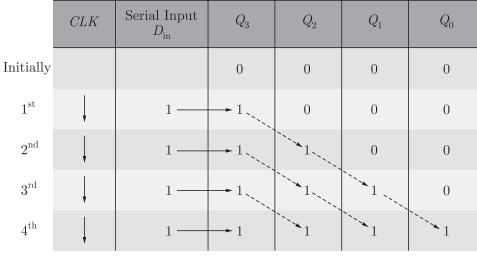

- 9.5 Serial-in Parallel-out Shift Register 584

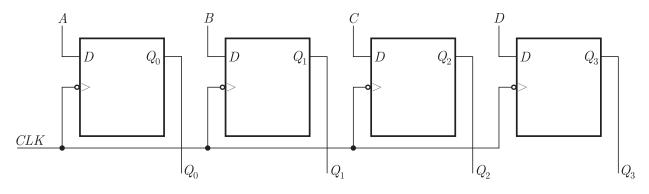

- 9.6 Parallel-in Serial-out Shift Register 585

- 9.7 Parallel-in Parallel-out Shift Register 586

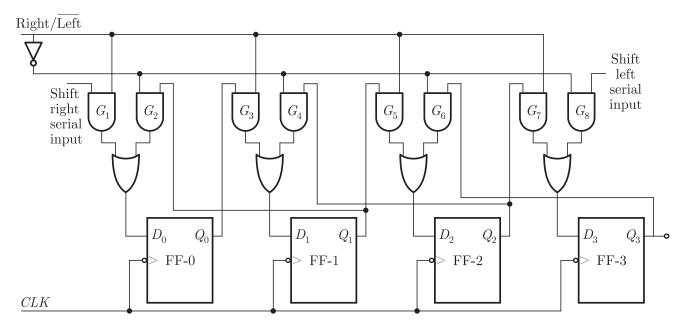

- 9.8 Bidirectional Shift Register 586

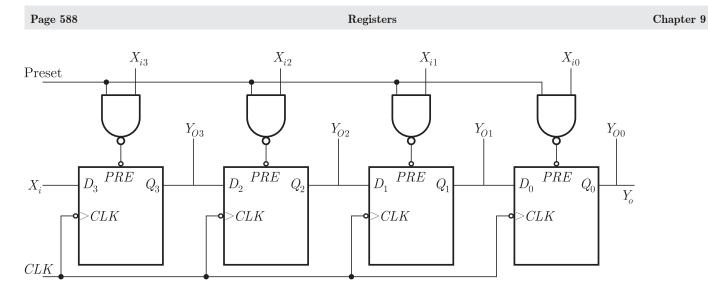

- 9.9 Universal Shift Register 587

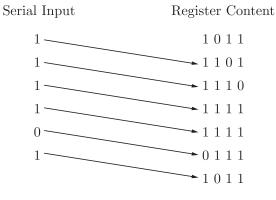

- 9.10 Applications of Shift Registers 588 Review Questions and Problems 598

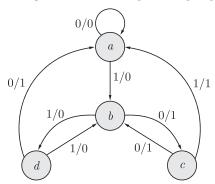

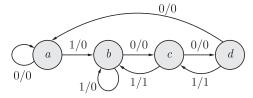

# 10 SEQUENTIAL CIRCUIT DESIGN

- 10.1 Introduction 599

- 10.2 Finite State Machine 599

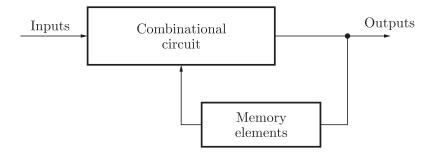

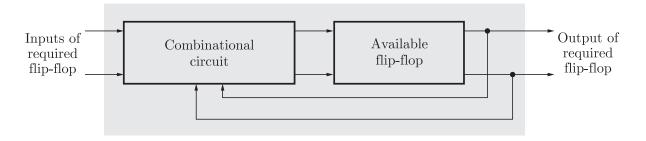

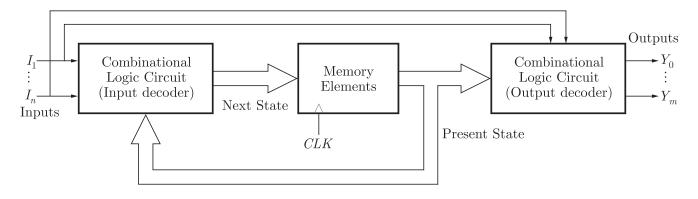

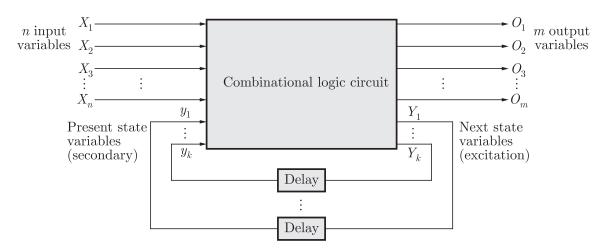

- 10.3 Model of a General Sequential Circuit 599

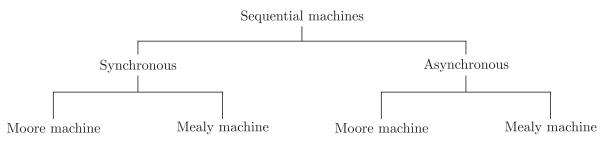

- 10.4 Classification of Sequential Circuits 600

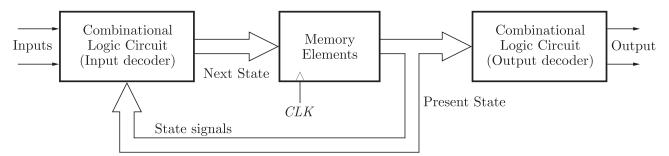

- 10.5 Models For Synchronous Sequential Circuits 601

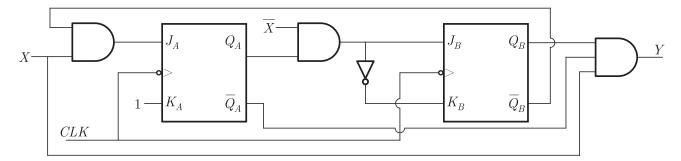

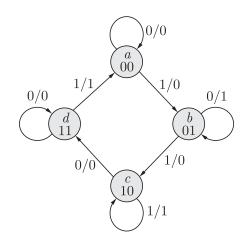

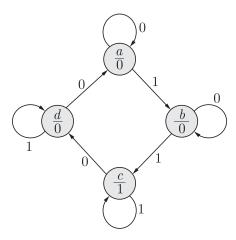

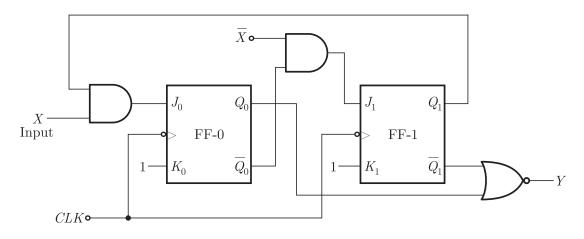

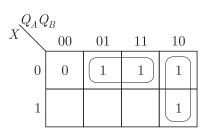

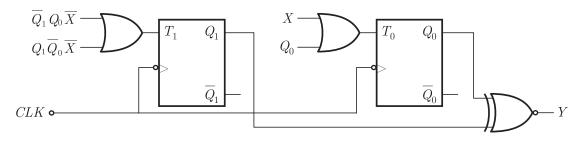

| 10.6  | Analysis of Clocked Sequential circuits 603               |

|-------|-----------------------------------------------------------|

| 10.7  | State Reduction and Assignment 609                        |

| 10.8  | Design Procedure of Clocked Sequential Circuits 613       |

| 10.9  | Design with Unused States 616                             |

| 10.10 | Lock-out Condition 618                                    |

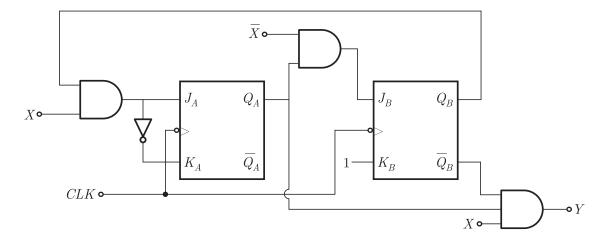

| 10.11 | The Sequence Detector 621                                 |

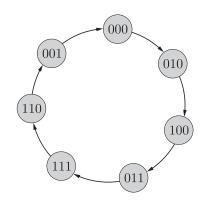

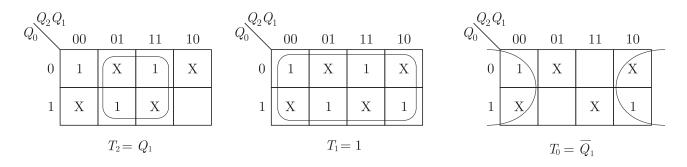

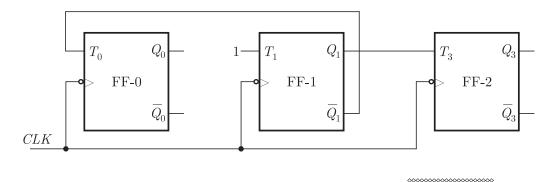

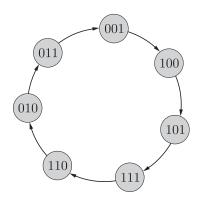

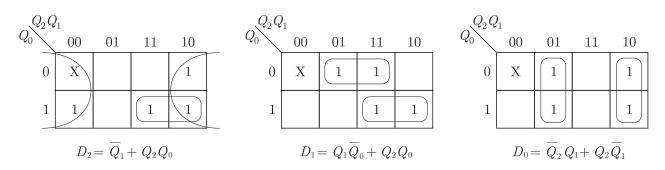

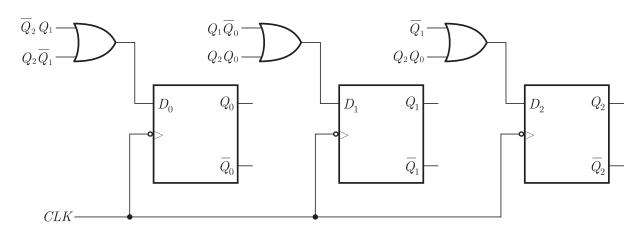

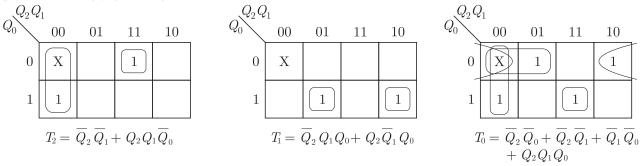

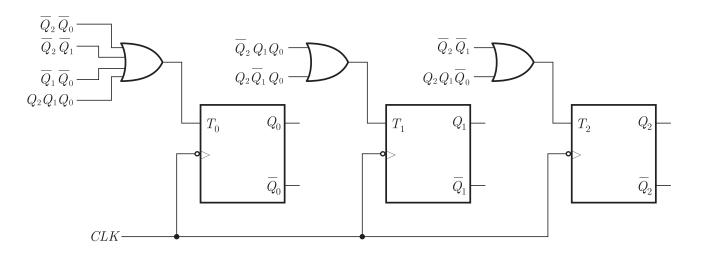

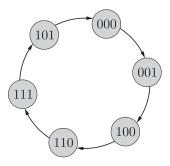

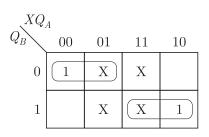

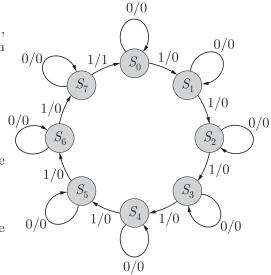

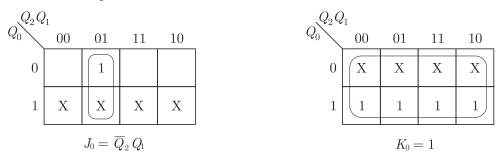

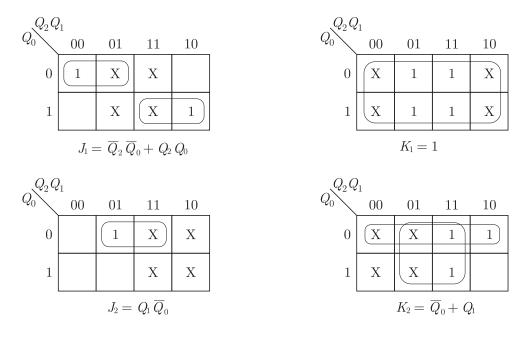

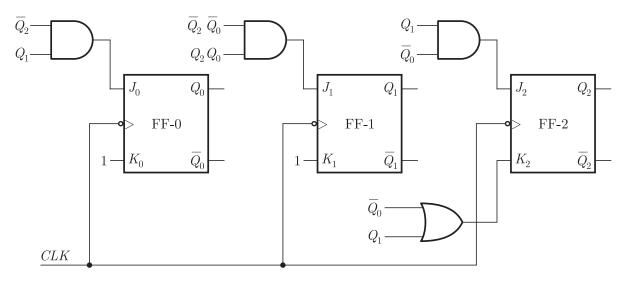

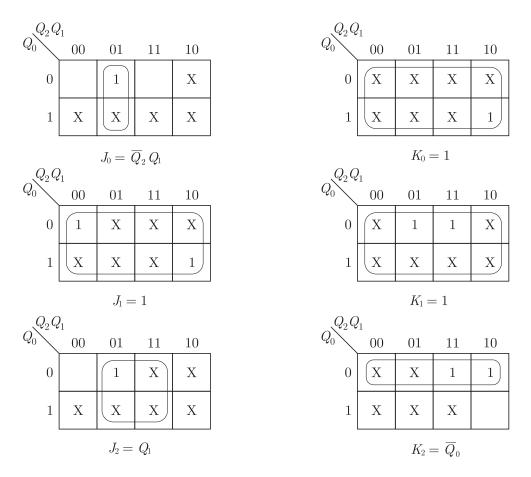

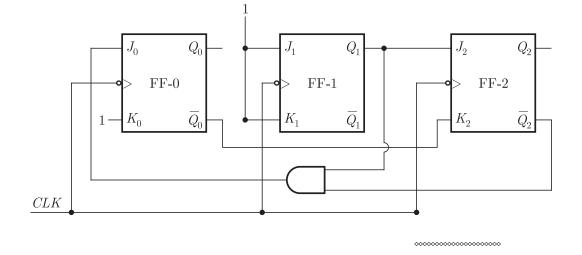

| 10.12 | Counter Design As Synchronous Sequential Circuit 624      |

| 10.13 | Asynchronous Sequential Circuit 630                       |

| 10.14 | Essential Hazards in Asynchronous Sequential Circuits 631 |

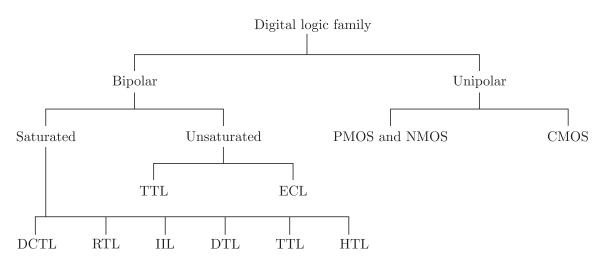

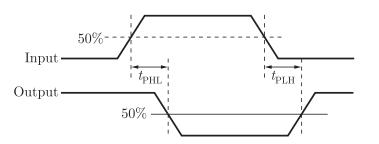

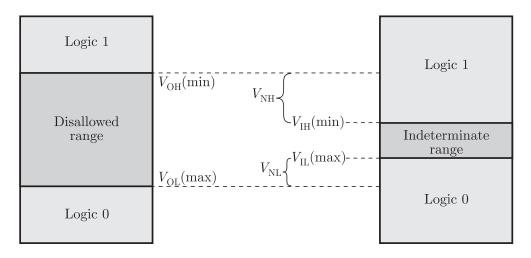

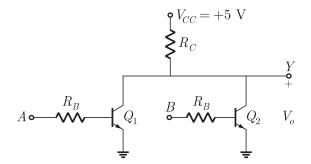

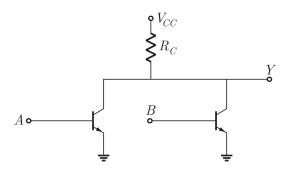

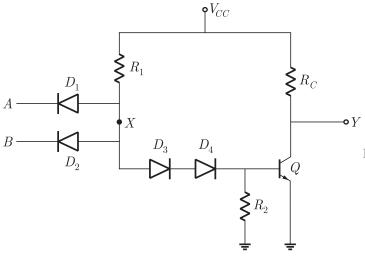

| DIGIT | AL LOGIC FAMILIES                                         |

| 11.1  | Introduction 647                                          |

| 11.2  | Classification of Digital Logic Family 647                |

| 11.3  | Characteristic Parameters of Digital Logic Family 649     |

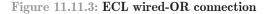

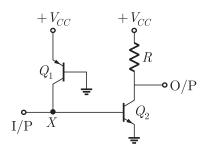

| 11.4  | Resistor-Transistor Logic $(RTL)$ 653                     |

| 11.5  | Direct Coupled Transistor Logic (DCTL) 654                |

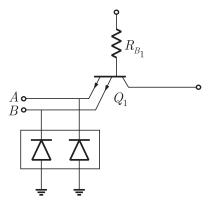

| 11.6  | Diode Transistor Logic (DTL) 655                          |

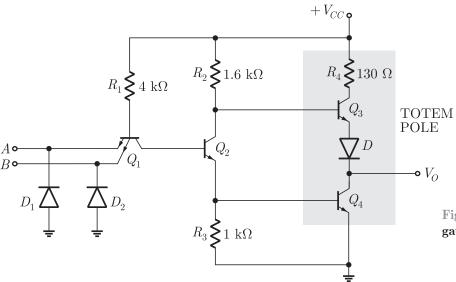

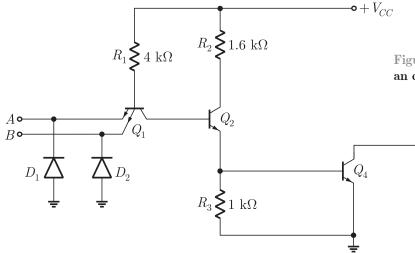

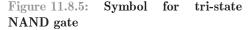

| 11.7  | Transistor-Transistor Logic $(TTL)$ 656                   |

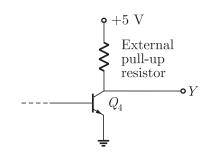

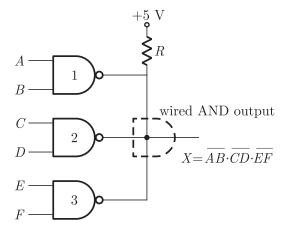

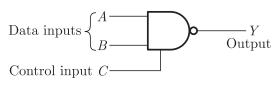

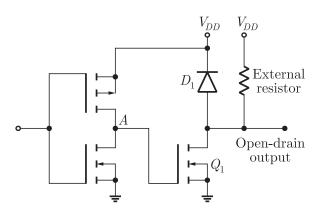

| 11.8  | TTL Circuit Output Connection 657                         |

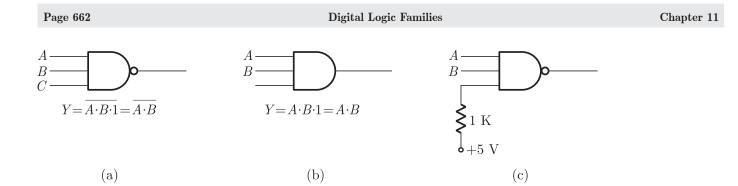

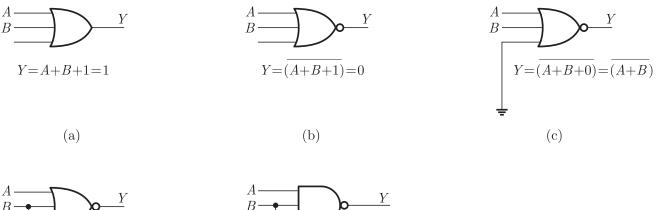

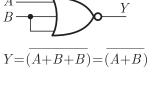

| 11.9  | TTL Parameters 662                                        |

| 11.10 | TTL Subfamilies 665                                       |

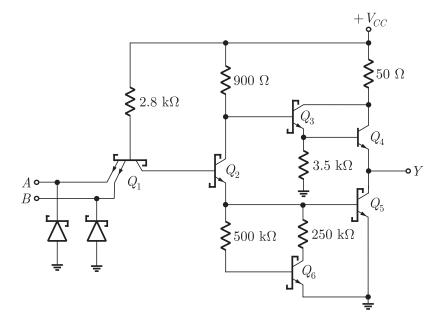

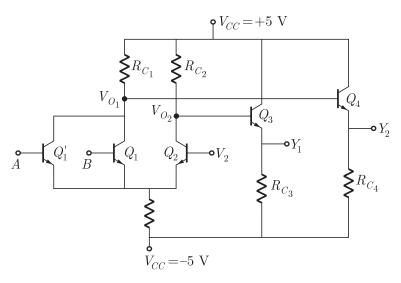

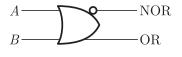

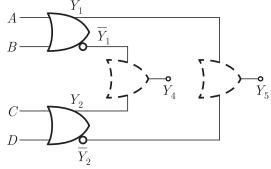

| 11.11 | Emitter Coupled Logic (ECL) 668                           |

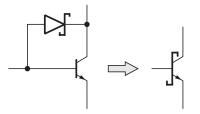

| 11.12 | Integrated Injection Logic $(I^2L)$ 670                   |

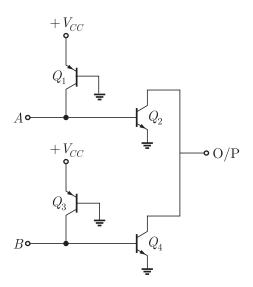

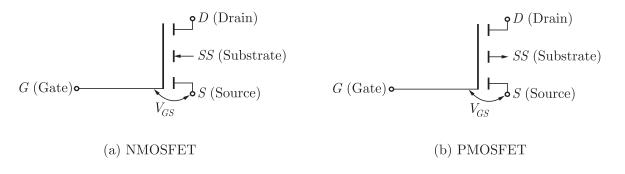

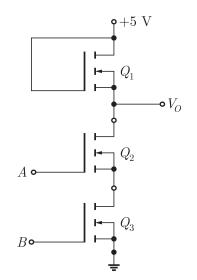

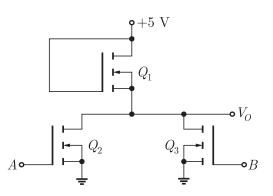

| 11.13 | Metal Oxide Semiconductor (MOS) Logic 672                 |

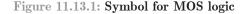

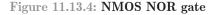

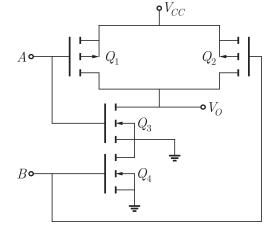

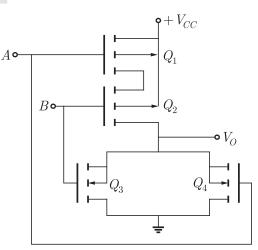

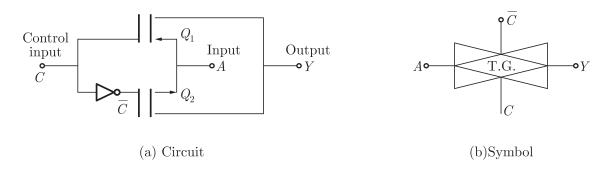

| 11.14 | Complementary Metal Oxide Semiconductor (CMOS) Logic      |

| 11.15 | Characteristics of CMOS Logic 679                         |

| 11.16 | Advantages and Disadvantages of CMOS Logic 680            |

| 11.17 | Comparison Between CMOS and TTL Families 680              |

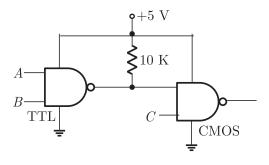

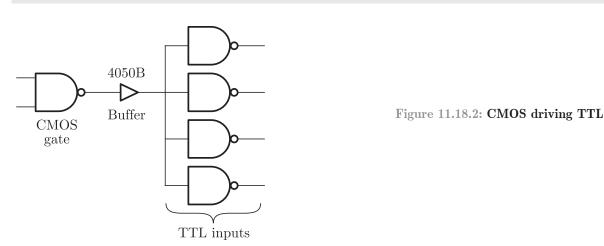

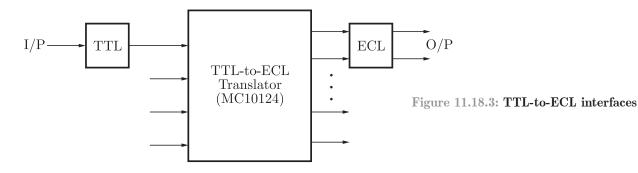

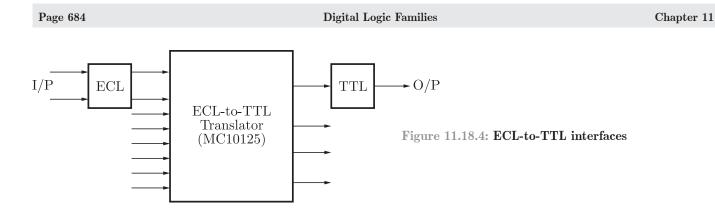

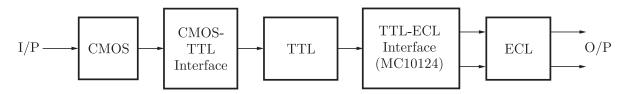

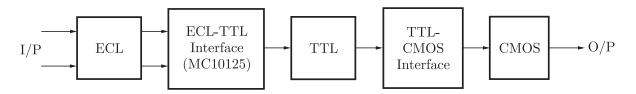

| 11.18 | Interfacing 681                                           |

| 11.19 | Comparison of Various Logic Families 685                  |

|       | Review Questions and Problems 686                         |

|       |                                                           |

\*\*\*\*\*\*\*

# NUMBER SYSTEMS

#### 1.1 INTRODUCTION

In this modern world of electronics, the term digital is mostly associated with a computer. Today, digital circuits and systems has a wide range of application in almost every field of electronics. In communications, the principles of digital electronics are found in satellites, telephone switching and transmission networks, and navigation systems. In consumer electronics, digital circuits are found in compact discs, VCRs, and television. Similarly, digital systems are also used in process controls in industrial applications and in the field of medical science.

In this chapter, we will begin the discussion with the introduction of digital and analog system and then we shall study different number systems used to represent data in digital systems.

## 1.2 ANALOG AND DIGITAL SYSTEMS

There are two types of electronic circuits and systems; analog and digital. Analog systems are those in which physical quantities are represented over a continuous range of values. They can take infinite values within the specified range. For example, the amplitude of the output signal to the speaker in a radio receiver can have any value between zero and its maximum limit.

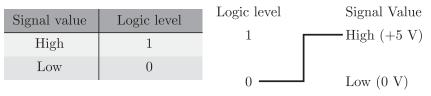

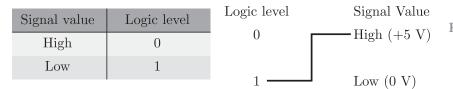

On the other hand, digital systems are those in which physical quantities are represented in digital form; that is, the quantities can take on only discrete values. Any quantity in the physical world, such as temperature, pressure, or voltage, can be symbolized in a digital circuit by a group of logic levels that, taken together, represent a binary number. Logic levels are usually specified as 0 or 1; at times, it may be more convenient to use low/high, false/true, or off/on.

#### **1.2.1** Advantages of Digital Systems

Following are some of the advantages of digital systems over analog systems:

#### Digital systems are easier to design

Since all the modern digital circuits use only two voltage levels, HIGH and LOW, hence they are easier to design. The exact numerical values of voltages are not important because they have only logical significance; only the range in which they fall is important. In analog

#### **READER NOTE**

Digital circuits are also called logic circuits, because each type of digital circuit obeys a certain set of logic rules. The manner in which a logic circuit responds to an input is referred to as the circuit logic. systems, signals have numerical significance; so, their design is more complex.

#### Storage of information is easy

The storage of digital information is easy because there are many types of semiconductor and magnetic memories of large capacity which can store digital data for periods as long a necessary.

#### Greater accuracy and precision

Digital systems are much more accurate and precise than analog systems, because digital systems can be expanded to handle more digits simply by adding more switching circuits. Analog systems are quite complex and costly for the same accuracy and precision.

# Digital systems are less affected by noise

Unwanted electrical signals are called noise. Since in analog systems the exact values of voltages are important and in digital systems only the range of values is important, the effect of noise is more critical in analog systems. In digital systems, noise is not critical as long as it is so large that we can not distinguishing a HIGH from a LOW.

#### Operation can be controlled by a program

It is quite easy to design digital systems whose operation is controlled by a set of stored instructions called a program. If we want to change the system operation, we can do it easily by modifying the program. The analog systems can also be programmed, but the variety of the available operations are limited.

# More digital circuitry can be fabricated on integrated circuit (IC) devices

The fabrication of digital ICs is simpler and economical compared to the analog ICs. Moreover, higher densities of integration can be achieved in digital ICs than in analog ICs, because digital design does not require high value capacitors, precision resistors, inductors and transformers (which cannot be integrated economically) like the analog design.

#### Digital System are more reliable

Digital systems are more reliable than analog systems.

# **1.2.2** Limitations of Digital Systems

We have already discussed the advantages digital systems, but there are some limitation of digital systems. In real world, most physical quantities are analog in nature. These quantities are used as input signals of system and monitored for controlling the system. In digital system these analog quantities are used through following steps:

- 1. Convert the analog inputs to digital form by a using analog to digital converted, ADC.

- 2. Process the digital information.

- 3. Convert the digital outputs back to analog form by digital to analog converter, DAC.

Because of these conversions, the processing time increases and the system becomes more complex. In most cases, these disadvantages are outweighed by numerous advantages of digital techniques.

#### 1.3 NUMBER SYSTEMS

Number system is one of the most basic topics in digital electronics. The knowledge of number systems is important to understand how data are represented before they can be processed by any digital system including a digital computer.

A number system is nothing more than a code that uses symbols to represent a number. In general, in any number system, there is an ordered set of symbols known as digits.

The most widely used number system is positional number system. In positional number system, a number is represented by a string of digits and each digit position has an associated weight. A number is made up of a collection of digits and it has two parts ; integer and fraction, both are separated by a radix point (.). The number is represented as,

$$\underbrace{\left(\frac{d_{n-1} d_{n-2} \dots d_{1} d_{0}}{\text{Integer part}} \stackrel{\uparrow}{\underset{\text{Radix}}{\underset{\text{point}}{\uparrow}}} \underbrace{d_{-1} d_{-2} \dots d_{-m}\right)_{r}}_{\text{Fractional part}}$$

where, r = radix or base of the number system

n = number of digits in the integer part

m = number of digits in fractional part

$d_{n-1} = \text{most significant digit (MSD)}$

$d_{-m} = \text{least significant digit (LSD)}$

#### Radix or Base (r)

The number of independent digits or symbols used in a number system, is known as radix or base of the number system.

All positional number systems must have a radix or base denoted as r. It is defined as the weight of a digit which depends on its relative position within the number. The weights of different digits in the integer part of the number are given by  $r^0$ ,  $r^1$ ,  $r^2$ ,  $r^3$ , and so on, starting with the digit adjacent to radix point. For the fractional part, these are  $r^{-1}$ ,  $r^{-2}$ ,  $r^{-3}$ , and so on, again starting with the digit next to the radix point.

The value of number is the sum of each digit multiplied by the corresponding power of the radix, given as

$$(N)_r = (d_{n-1} \times r^{n-1}) + (d_{n-2} \times r^{n-2}) + \dots + (d_1 \times r^1) + (d_0 \times r^0) + (d_{-1} \times r^{-1}) + (d_{-2} \times r^{-2}) + \dots + (d_{-m} \times r^{-m})(1.3.1)$$

where d is the integer in the range  $0 \le d_i \le (r-1)$ . On the basis of number of different symbols used (radix), number systems are classified as, (i) decimal number system, (ii) binary number (iii) octal number system, and (iv) hexadecimal number system. Now, we discuss each number system in following sections.

#### SIGNIFICANCE OF RADIX

It is important to note that, maximum numbers that can be written with n digits in a given number system are equal to  $r^n$ , where r is the base or radix.

#### DO REMEMBER

The value obtained by Eq. (1.3.1) is simply equivalent decimal value of the number.

#### 1.3.1 Decimal Number System

The decimal number system is a radix 10 number system and therefore has 10 different digits or symbols to represent a number. These are 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9. All higher numbers after '9' are represented in terms of these 10 digits only. The radix point is known as the decimal point.

The weights of different digits in a mixed decimal number, starting from the decimal point, are  $10^{\circ}$ ,  $10^{1}$ ,  $10^{2}$ , and so on for the integer part and  $10^{-1}$ ,  $10^{-2}$ ,  $10^{-3}$ , and so on for the fractional part. The value of a given decimal number can be expressed as a sum of various digits multiplied by their place values or weights. For example,

$(145.86)_{10} = 1 \times 10^{2} + 4 \times 10^{1} + 5 \times 10^{0} + 8 \times 10^{-1} + 6 \times 10^{-2}$ = 100 + 40 + 5 + 0.8 + 0.06= 145.86

# 1.3.2 Binary Number System

Binary number system is a radix-2 number system with '0' and '1' as the two independent digits. All larger binary numbers are represented in terms of '0' and '1'. The radix point is known as the binary point. These symbols are known as bits (binary digits). It is a positional number system; the weight of a bit is defined by its position with base 2.

Starting from the binary point, the weights of different digits in a mixed binary number are  $2^0$ ,  $2^1$ ,  $2^2$ , and so on for the integer part and  $2^{-1}$ ,  $2^{-2}$ ,  $2^{-3}$ , and so on for the fractional part.

For example,

$$(1011.101)_2 = 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0 + 1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-3}$$

#### Advantages

- 1. The binary number system is used in digital computers because the basic electronics devices used in these computers can be conveniently and efficiently operated in two distinctly different modes. For example, a bipolar transistor could be operated either in the cut-off or in saturation very efficiently.

- 2. The another advantage of this number system is that all kinds of data could be conveniently represented in terms of 0's and 1's.

- 3. Lastly, the circuits required for performing arithmetic operations such as addition, subtraction, multiplication, division, etc. become simpler when the data involved are represented in the binary number system.

#### **1.3.3** Octal Number System

The octal number system has a radix of 8 and therefore has 8 digits to represent a number. The independent digits are 0, 1, 2, 3, 4, 5, 6, and 7. All higher order numbers are expressed as a combination of these

The process of writing higher order numbers after 9 consists of writing the second digit, that is 1, first and then following it up with other digits, one by one, to obtain the next 10 numbers from 10 to 19. The next 10 numbers from 20 to 29 are obtained by writing the third digit, that is 2, first and then following it with digits 0 to 9 one by one. The process continues till we have used all possible twodigit combinations and reached 99.

**COUNTING IN DECIMAL NUMBER SYSTEM**

#### **COUNTING IN BINARY NUMBER SYSTEM**

The procedure for writing higher order binary numbers after 1 is similar to the one explained in case of decimal number system. For example, the first 16 numbers in the binary number system would be 0, 1, 10, 11, 100, 101, 110, 111, 1000, 1001, 1010, 1011, 1100, 1101, and 1111. The also proves the point made earlier that a maximum of only  $16(=2^4)$  numbers could be written with four digits(bits).

#### Page 4

# 1.4 NUMBER SYSTEM CONVERSION

We know that computer systems process binary data, but the information given by the user may be in the form of decimal number, hexadecimal number, or octal number. So it is required to study the conversion of the numbers from one number system to another.

Since there are 3 independent digits in the given number system, radix is 3. The counting process is same as that of other number systems described above. First 10 numbers are as follows 0, 1, X, 10,

# 1.4.1 Finding the Decimal Equivalent

The decimal equivalent of a given number in another number system is given by the sum of all the digits multiplied by their respective position weight. We can use Eq. (1.3) to obtain decimal equivalent of a number represented in any base r, that is

$$(N)_{r} = (d_{n-1} \times r^{n-1}) + (d_{n-2} \times r^{n-2}) + \dots + (d_{1} \times r^{1}) + (d_{0} \times r^{0}) + (d_{-1} \times r^{-1}) + (d_{-2} \times r^{-2}) + \dots + (d_{-m} \times r^{-m})(1.3.1)$$

Binary-to-decimal, octal-to-decimal, and hexadecimal-todecimal conversions are illustrated in the following sections with the help of examples.

# **Binary-to-Decimal Conversion**

For binary number system, base r = 2. So we substitute r = 2 into Eq. (1.3) to obtain decimal equivalent of any binary number represented as  $(d_n d_{n-1} d_{n-2} \dots d_1 d_0 \dots d_{-1} d_{-2} \dots d_{-m})$ .

$$(N)_{10} = (d_{n-1} \times 2^{n-1}) + (d_{n-2} \times 2^{n-2}) + \dots + (d_1 \times 2^1) + (d_0 \times 2^0) + (d_{-1} \times 2^{-1}) + (d_{-2} \times 2^{-2}) + \dots + (d_{-m} \times 2^{-m})$$

For example, the decimal equivalent of a binary number 110101 can be obtained as,

$$(110101)_2 = (1 \times 2^5) + (1 \times 2^4) + (0 \times 2^3) + (1 \times 2^2) + (0 \times 2^1) + (1 \times 2^0) = 32 + 16 + 0 + 4 + 0 + 1 = (53)_2$$

Similarly, we can convert the binary number 11101.1011 into equivalent decimal number as follows

$$\begin{aligned} (11101.1011)_2 &= (1 \times 2^4) + (1 \times 2^3) + (1 \times 2^2) + (0 \times 2^1) \\ &+ (1 \times 2^0) + (1 \times 2^{-1}) + (0 \times 2^{-2}) + (1 \times 2^{-3}) + (1 \times 2^{-4}) \\ &= 16 + 8 + 4 + 0 + 1 + 0.5 + 0 + 0.125 + 0.0625 \\ &= (29.6875)_{10} \end{aligned}$$

# **Octal-to-Decimal Conversion**

For octal number system, base r = 8. So we substitute r = 8 into Eq. (1.3) to obtain decimal equivalent of any octal number represented as  $(d_n d_{n-1} d_{n-2} \dots d_1 d_0 \dots d_{-1} d_{-2} \dots d_{-m})$ . Therefore,

The value obtained by Eq. (1.3.1) is simply equivalent decimal value of the number represented in any base r.

DO REMEMBER

**SOLUTION**:

11, 1X, X0, X1, XX, 100.

Chapter 1

$$(N)_{10} = (d_{n-1} \times 8^{n-1}) + (d_{n-2} \times 8^{n-2}) + \dots + (d_1 \times 8^1) + (d_0 \times 8^0) + (d_{-1} \times 8^{-1}) + (d_{-2} \times 8^{-2}) + \dots + (d_{-m} \times 8^{-m})$$

For example, the decimal equivalent of octal number  $(4057.06)_s$  can be obtained as

$$(4057.06)_8 = 4 \times 8^3 + 0 \times 8^2 + 5 \times 8^1 + 7 \times 8^0 + 0 \times 8^{-1} + 6 \times 8^{-2}$$

= 2048 + 0 + 40 + 7 + 0 + 0.0937 = (2095.0937)<sub>10</sub>

#### Hexadecimal-to-Decimal Conversion

For hexadecimal number system, base r = 16. So we substitute r = 16 into Eq. (1.3) to obtain decimal equivalent of any hexadecimal number represented as  $(d_n d_{n-1} d_{n-2} \dots d_1 d_0 \dots d_{-1} d_{-2} \dots d_{-m})$ .

$$(N)_{10} = (d_{n-1} \times 16^{n-1}) + (d_{n-2} \times 16^{n-2}) + \dots + (d_1 \times 16^1) + (d_0 \times 16^0) + (d_{-1} \times 16^{-1}) + (d_{-2} \times 16^{-2}) + \dots + (d_{-m} \times 16^{-m})$$

For example, the decimal equivalent of hexadecimal number  $(5C7)_{16}$  can be obtained as

$$(5C7)_{16} = (5 \times 16^{2}) + (12 \times 16^{1}) + (7 \times 16^{0}) = 1280 + 192 + 7 = (1479)_{10}$$

#### 1.4.2 Decimal-to-Binary Conversion

The most common method to convert a decimal number to a binary number is known as repeated division and multiplication method. In this method the integer and fractional parts of a decimal number are treated separately for the conversion.

For the integer part, the binary equivalent can be found by successively dividing the integer part of the number by 2, and for the fractional part, it is found by successively multiplying the fractional part of the decimal number by 2. This is also known as the doubledabble method.

#### Integer part Conversion (Repeated Division Method)

In the repeated division method, the decimal number is divided by 2 and the remainder is found after each division, until the quotient 0 is obtained. The last remainder is the MSB. The remainders read from bottom to top give the equivalent binary integer number.

For example, the binary equivalent of decimal number  $(25)_{10}$  can be obtained as

|             | Quotient | Remainder |               |

|-------------|----------|-----------|---------------|

| $25 \div 2$ | 12       | 1         | • LSB         |

| $12 \div 2$ | 6        | 0         |               |

| $6 \div 2$  | 3        | 0         |               |

| $3 \div 2$  | 1        | 1         |               |

| $1 \div 2$  | 0        | $1 \mid$  | $\bullet$ MSB |

|             |          |           |               |

$(25)_{10} = (11001)_2$

Hence,

Page 7

Page 8

# Fractional part Conversion (Repeated Multiplication Method)

In the repeated multiplication method, the fractional part of the decimal number is multiplied by 2; the integer part of the multiplication is found after each multiplication operation, until the fractional part of a decimal number becomes zero. The first integer is the MSB. Thus, the integers read from top to bottom give the equivalent binary fraction.

For example, the binary equivalent of decimal number  $(0.625)_{10}$  can be obtained as

| Multiplication | Integer 1   | oart |

|----------------|-------------|------|

| maniphoanon    | Introport 1 | Jun  |

| $0.625 \times 2 = 1.25$ | 1 | • MSB |

|-------------------------|---|-------|

| $0.25 \times 2 = 0.5$   | 0 |       |

| $0.5 \times 2 = 1.0$    | 1 | • LSB |

Hence,  $(0.625)_{10} = (0.101)_2$

#### EXAMPLE 1.2

Convert the decimal number  $(57.825)_{10}$  to its equivalent binary,

# SOLUTION :

The integer part of this decimal number is 57 and the fractional part is 0.825. The decimal to binary equivalent can be obtained as follows:

# Conversion of integer part :

|             | Quotient | Remainder |               |

|-------------|----------|-----------|---------------|

| $57 \div 2$ | 28       | 1         | $\bullet$ LSB |

| $28 \div 2$ | 14       | 0         |               |

| $14 \div 2$ | 7        | 0         |               |

| $7 \div 2$  | 3        | 1         |               |

| $3 \div 2$  | 1        | 1         |               |

| $1 \div 2$  | 0        | 1         | $\bullet$ MSB |

Hence,  $(57)_{10} = (111001)_2$

# Conversion of fractional part :

| Multiplication           | Integer part |               |

|--------------------------|--------------|---------------|

| $0.825 \times 2 = 1.650$ | 1            | • MSB         |

| $0.650 \times 2 = 1.30$  | 1            |               |

| $0.30 \times 2 = 0.6$    | 0            |               |

| $0.6 \times 2 = 1.2$     | 1            | $\bullet$ LSB |

Note that multiplication process goes continue, so we obtain the result up to bits only.

#### DO REMEMBER

If the result of multiplication does not seem to be resulting into zero, the process may be continued till the desired accuracy or required number of bits are obtained.

#### CONVERSION OF MIXED NUMBERS

To convert a mixed number to binary, convert the integer and fraction parts separately to binary and then combine them. Page 10

result 0. So, consider the conversion up to 5 bits only.

Hence,  $(0.201)_{10} = (0.14672)_8$ Combining result of integer and fractional parts, we get the equivalent octal number.

$(125.201)_{10} = (175.14672)_{8}$

# 1.4.4 Decimal-to-Hexadecimal Conversion

The process of decimal-to-hexadecimal conversion is also similar as the two conversion discussed earlier. Again, the integer and fractional parts of the decimal number are treated separately.

To convert the given decimal integer number to hexadecimal, successively divide the given number by 16 till the quotient is 0. The last remainder is the MSD. The remainders read from bottom to top give the equivalent octal integer number.

To convert the given decimal fraction to hexadecimal, successively multiply the decimal fraction and the subsequent decimal fractions by 16 till the product is 0 or till the required accuracy is obtained. The first integer from the top is the MSD. Thus, the integers read from top to bottom give the equivalent octal fraction.

#### **EXAMPLE 1.4**

Convert the decimal number  $(125.201)_{10}$  to its equivalent hexadecimal number.

## SOLUTION :

The integer part of  $(125.201)_{10}$  is 125 and the fractional part is 0.201.

#### **Conversion of integer part :**

|               | Quotient | Remainder |     |       |

|---------------|----------|-----------|-----|-------|

|               |          | Decimal   | Hex |       |

| $125 \div 16$ | 7        | 13        | D   | • LSD |

| $7 \div 16$   | 0        | 7         | 7   | • MSD |

Hence,  $(125)_{10} = (7D)_8$

**Conversion of fractional part :**

|                            | Integer |     |       |

|----------------------------|---------|-----|-------|

|                            | Decimal | Hex |       |

| $0.201 \times 16 = 3.216$  | 3       | 3   | • MSD |

| $0.216 \times 16 = 3.456$  | 3       | 3   |       |

| $0.456 \times 16 = 7.296$  | 7       | 7   |       |

| $0.296 \times 16 = 4.736$  | 4       | 4   |       |

| $0.736 \times 16 = 11.776$ | 11      | В   | • LSD |

#### DO REMEMBER

The process of decimal to hexadecimal conversion is same as decimal to binary and decimal to octal conversion, except that in this case repeated multiplication and division are by 16 which is the base of hexadecimal number system.

#### 1.4.6 **Binary-to-Octal Conversion**

A binary number can be converted into an equivalent octal number by splitting the integer and fractional parts into groups of three bits, starting from the binary point on both sides. Then, replace each 3-bit binary group by the equivalent octal digit given in Table 1.4.1 The 0's can be added to complete the outside groups if required.

#

#### 1.4.7 Hexadecimal-to-Binary Conversion

To convert a hexadecimal number to binary, replace each hex digit by its 4-bit binary equivalent. So, we just have to remember the 4-bit binary equivalents of the basic digits of the hexadecimal number system, given in Table 1.4.2.

| Table 1.4.2: | Hexadecimal | digit and | its binary | equivalent |

|--------------|-------------|-----------|------------|------------|

|              |             |           |            |            |

| Hexadecimal | Binary | Hexadecimal | Binary |

|-------------|--------|-------------|--------|

| 0           | 0000   | 8           | 1000   |

| 1           | 0001   | 9           | 1001   |

#### **CONFUSION CLEARING**

Note that for integer part we start making group of 3-bits from left to right and for the fractional part we make groups started from right to left. We can add 0's on the extreme left of the integer part or extreme right of the fractional part to complete a 3-bit group.

Digital Electronics by Ashish Murolia and RK Kanodia For More Details visit www.nodia.co.in

#### Page 14

Convert the following binary numbers to their hexadecimal equivalents. (a) (1011011011),

(b) (0.010011011)<sub>2</sub>

(c) (1011001110.01111),

# **SOLUTION**:

For conversion to hexadecimal, we make group of 4-bits, and replace each 4-bit group by a hexadecimal digit.

(a) (1011011011)<sub>2</sub>

| Given binary number :                                                      | 1011011011                                                                                            |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Groups of 4-bits :                                                         | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                  |

|                                                                            | 2 D B                                                                                                 |

| Hexadecimal equivalent :                                                   | $(2DB)_{16}$                                                                                          |

| Thus, $(1011011011)_2 =$                                                   | = (2DB) <sub>16</sub>                                                                                 |

| (b) $(0.010011011)_2$                                                      |                                                                                                       |

| Given binary number :                                                      | 0.010011011                                                                                           |

| Groups of 4-bits :                                                         | 0.010011011000                                                                                        |

|                                                                            | 4 D 8                                                                                                 |

| Hexadecimal equivalent :                                                   | $(4D8)_{16}$                                                                                          |

| Thus, $(0.010011011)_2 =$                                                  | $= (4D8)_{16}$                                                                                        |

| (c) $(1011001110.011111)_2$                                                |                                                                                                       |

| Given binary number :                                                      | 1011001110.011111                                                                                     |

| Groups of 4-bits :                                                         | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                  |

|                                                                            | $2$ C E $\cdot$ 7 C                                                                                   |

| Hexadecimal equivalent :                                                   | $(2CE.7C)_{16}$                                                                                       |

| (c) $(1011001110.011111)_2$<br>Given binary number :<br>Groups of 4-bits : | $\begin{array}{c} 1011001110.011111\\ \underline{0010} \\ 2 \\ C \\ E \\ \cdot \\ 7 \\ C \end{array}$ |

Thus,  $(1011001110.01111)_2 = (2CE.7C)_{16}$

# 1.4.9 Hexadecimal-to-Octal and Octal-to-Hexadecimal Conversion

To convert a hexadecimal number to octal, the easiest way is to first convert the given hexadecimal number to binary and then the binary number to octal.

Similarly, to convert an octal number to hexadecimal, first convert the given octal number to binary and then the binary number to hexadecimal. Two types of conversion are illustrated in the following example.

- (a) An integer decimal number can be converted to any other base r, by repeatedly dividing the given decimal number by r until the quotient becomes zero. The remainders written from bottom to top gives the equivalent.

- (b) A fractional decimal number can be converted to any other base r, by repeatedly multiplying the given decimal number by r until a number with zero fractional part is obtained. The integer parts of multiplication taken from top to bottom gives the equivalent.

- 3(a). To perform octal-to-binary conversion, replace each digit in the octal number with its three-bit binary equivalent. For binary-to-octal conversion, split the binary number into groups of three bits, starting from the binary point, and, if needed, complete the outside groups by adding 0's, and then write the octal equivalent of these three-bit groups.

- (b) Similarly, for hexadecimal-binary conversion, replace each hex digit with its four-bit binary equivalent. For binary-tohexadecimal conversion, split the binary number into groups of four bits, starting from the binary point, and, if needed, complete the outside groups by adding 0's, and then write the hex equivalent of the four-bit groups.

- 4(a). For hexadecimal-to-octal conversion, first we convert the given hexadecimal number into its binary equivalent and further this binary number converted into its octal equivalent.

- (b) For octal-to-hexadecimal conversion, the octal number may first be converted into an equivalent binary number and then the binary number transformed into its hexadecimal equivalent.

#### EXAMPLE 1.10

Convert the following numbers to their decimal equivalents. (a)  $(11101.1011)_2$  (b)  $(651.7)_8$  (c)  $(EF9.B)_{16}$

#### SOLUTION :

Thus,  $(EF9.B)_{16} = (3833.675)_{10}$

#### DO REMEMBER

If the result of multiplication does not seem to be resulting into zero, the process may be continued till the desired accuracy or required number of bits are obtained. Thus,

#### Conversion of fractional Part:

| Multiplication          | Integer part |               |

|-------------------------|--------------|---------------|

| $0.815 \times 8 = 6.52$ | 6            | • MSD         |

| $0.52 \times 8 = 4.16$  | 4            |               |

| $0.16 \times 8 = 1.28$  | 1            | $\bullet$ LSD |

$(543)_{10} = (1037)_{8}$

So on

Thus,  $(0.815)_{10} = (0.641)_8$ Combining results of integer and fractional part, we get

$(543.815)_{10} = (1037.641)_{8}$

(c) The integer part of the number  $(683.275)_{10}$  is 683 and fractional part is 0.275.

#### **Conversion of Integer Part:**

|               | Quotient | Remai   | nder |   |                        |

|---------------|----------|---------|------|---|------------------------|

|               |          | Decimal | Hex  |   |                        |

| $683 \div 16$ | 42       | 11      | В    | t | • LSD                  |

| $42 \div 16$  | 2        | 10      | А    |   |                        |

| $2 \div 16$   | 0        | 2       | 2    |   | $\bullet~\mathrm{MSD}$ |

Thus,  $(683)_{10} = (2AB)_{16}$ Conversion of fractional part

| Multiplication          | Integer | part |       |

|-------------------------|---------|------|-------|

|                         | Decimal | Hex  |       |

| $0.275 \times 16 = 4.4$ | 4       | 4    | • MSD |

| $0.4 \times 16 = 6.4$   | 6       | 6    | • LSD |

Thus,  $(0.275)_{10} = (0.46)_{16}$ Combining results of integer and fractional part, we get

$(683.275)_{10} = (2AB.46)_{16}$

# EXAMPLE 1.12

Convert the octal number  $(527.64)_8$  to its binary equivalent and the binary number  $(11011101111001.011111)_2$  to its octal equivalent.

# **SOLUTION**:

To perform octal-to-binary conversion, we replace each octal digit with its 3-bit binary equivalent.

\*\*\*\*\*

operations such as binary addition, binary subtraction, binary multiplication, and binary division.

#### **1.6.1** Binary Addition

The rules of binary addition are as following:

0+0 = 0 1+0 = 1 0+1 = 1 1+1 = 0 and a carry 1 (i.e. 10 in binary) 1+1+1 = 1 and carry 1 (i.e. 11 in binary)

The addition of two binary numbers is performed columnwise exactly in the same manner as the addition of decimal numbers. When the binary numbers are more than one bit, the addition takes place bit by bit, which starts from left side. If the sum in one column is a two-bit number, the least significant bit is written as part of the total sum and the most significant bit is carried to the next left column as carry. An example of binary addition is given below.

#### EXAMPLE 1.14

Add the binary numbers 1101.101 and 111.011.

#### **SOLUTION**:

| $8\ 4\ 2\ 1\ .\ 2^{\overline{-1}}\ 2^{\overline{-2}}\ 2^{\overline{-3}}$ | • (Column numbers) |

|--------------------------------------------------------------------------|--------------------|

| $1\ 1\ 0\ 1\ .\ 1\ 0\ 1$                                                 | $\bullet A$        |

| $1\ 1\ 1\ .\ 0\ 1\ 1$                                                    | $\bullet B$        |

| 111 1 1                                                                  | • Carry            |

| 111 0 0 0                                                                | • $A+B$            |

We perform column by column addition as explained below: In the  $2^{-3}$ 's column:

1+1=0, with a carry of 1 to the  $2^{-2}$  column In the  $2^{-2}$ 's column:

0+1+1=0, with a carry of 1 to the  $2^{-1}$  column In the  $2^{-1}$ 's column:

1+0+1=0, with a carry of 1 to the 1's column In the 1's column:

1+1+1=1, with a carry of 1 to the 2's column In the 2's column:

0+1+1=0, with a carry of 1 to the 4's column In the 4's column:

1+1+1=1, with a carry of 1 to the 8's column In the 8's column:

1 + 1 = 0, with a carry of 1 to the 16's column

# **1.6.2** Binary Subtraction

The rules for binary subtraction are as following:

- 0 0 = 01 - 0 = 1

- 1 1 = 0

- 0-1 = 1 with a borrow of 1

The substraction of two binary numbers is also performed columnwise exactly in the same manner as the substraction of decimal numbers. When the binary numbers are more than one bit, the substraction takes place bit by bit, starting from left side(LSB). When 1 is subtracted from 0, we borrow a 1 from the next higher significant bit. The following examples illustrate the subtraction of two binary number.

#### **EXAMPLE 1.15**

Subtract 111.111 from 1010.01.

#### SOLUTION :

| $8\ 4\ 2\ 1\ .\ \bar{2^{-1}}\ \bar{2^{-2}}\ \bar{2^{-3}}$ | • (Column numbers)    |

|-----------------------------------------------------------|-----------------------|

| $1\ 0\ 1\ 0\ .\ 0\ 1\ 0$                                  | $\bullet A$           |

| $1\ 1\ 1\ .\ 1\ 1\ 1$                                     | $\bullet B$           |

| 1 1 1 1 1 1 1                                             | • Borrow              |

| $0\ 0\ 1\ 0\ .\ 0\ 1\ 1$                                  | • <i>A</i> - <i>B</i> |

We perform the column by column subtraction as explained below:

| Therefore, in the $2^{-3}$ column, | 10 - 1 = 1 |

|------------------------------------|------------|

| In the $2^{-2}$ 's column          | 10 - 1 = 1 |

| In the $2^{-1}$ 's column          | 1 - 1 = 0  |

| In the 1's column                  | 1 - 1 = 0  |

| In the 2's column                  | 10 - 1 = 1 |

| In the 4's column                  | 1 - 1 = 0  |

| In the 8's column                  | 0 - 0 = 0  |

| Hence, the result is $0010.011_2$  |            |

#### Explanation:

In the  $2^{-3}$  column, a 1 cannot be subtracted from a 0. So, borrow a 1 from the  $2^{-2}$  column making the  $2^{-2}$  column 0. The 1 borrowed from the  $2^{-2}$  column becomes 10 in the  $2^{-3}$  column.

In the  $2^{-2}$  column, a 1 cannot be subtracted from a 0. So, borrow a 1 from the  $2^{-1}$  column, but it is also a 0. So, borrow a 1 from the 1's column. That is also a 0, so borrow a 1 from the 2's column making the 2's column 0. This 1 borrowed from the 2's column becomes 10 in the 1's column. Keep one 1 in the 1's column, bring the other 1 to the  $2^{-1}$  column, which becomes 10 in this column. Keep one 1 in the  $2^{-1}$  column and bring the other 1 to the  $2^{-2}$  column, which becomes 10 in this column. Therefore,

Now, in the 2's column, a 1 cannot be subtracted from a 0;

#### READER NOTE

In 0-1, the result is negative. It indicates that the second number is greater than the first one. Similar to decimal number system, a borrow is generated.

#### **READER NOTE**

There are another methods of binary subtraction know as 1's and 2's complements methods. These methods are better than conventional method and discussed latter on.

#### Chapter 1

**EXAMPLE 1.17** Divide (11011011), by (110),

#### SOLUTION :

$$\begin{array}{r}

1 0 0 1 0 . 1 \\

1 1 0 1 1 0 1 1 0 1 1 \\

1 1 0 1 1 0 1 1 \\

1 1 0 \\

1 1 0 \\

1 1 0 \\

1 1 0 \\

1 1 0 \\

1 1 0 \\

0 0 0 \\

\end{array}$$

Thus,  $(11011011)_2 \div (110)_2 = (10010.1)_2$

#### Explanation:

Diviser 110 can go in 110, one time with a remainder of 0. Next bit is 1, 110 can not go in 1 so we take another next bit and put 0 in quotient. Now we have 11. Again 110 can not go in 11, so we take another next bit 0 and put 0 in quotient. Now we have 110. 110 can go in 110, one time with a remainder 0. Similarly we can perform the complete division operation.

#### \*\*\*\*\*\*

#### 1.7 COMPLEMENTS OF NUMBERS

Complements are used in digital systems to simplify the subtraction operation. For each base-r system there are two useful types of complements, the r's-complement, and the (r-1)'s-complement. These are also referred to as the radix complement and the diminished radix complement respectively.

Accordingly, for the base-10(decimal) system we have the 10's -complements and the 9's-complements, for the base-2(binary) system we have the 2's-complements and 1's-complements, for the base-8(octal) system we have the 8's-complements and 7's-complements, and for the base-16 we have the 16's-complements and the 15's-complements. We consider each in next sections.

# 1.7.1 Diminished Radix Complement or (r-1)'s Complement

Consider a number N in base-r system having n digits, then the (r-1)'s complement of N is defined as  $(r^n-1)-N$ .

For decimal number, r = 10 and r - 1 = 9, so the 9's complement of N is  $(10^n - 1) - N$ . In this case,  $10^n$  represents a number that consists of single 1 followed by n 0's.  $10^n - 1$  is a number represented by n 9's. For example, if n = 4, we have  $10^4 = 10,000$  and  $10^4 - 1 = 9999$ . Hence, it follows that the 9's complement of a

decimal number is obtained by subtracting each digit from 9. For example; the 9's complement of 645800 is 999999 - 645800 = 354199.

For binary numbers, r = 2 and r - 1 = 1, so the 1's complement of N is  $(2^n - 1) - N$ . Again,  $2^n$  is represented by a binary number that consists of a 1 followed by n 0's. $2^n - 1$  is a binary number represented by n 1's. For example, if n = 4, we have  $2^4 = (10000)_2$ and  $2^4 - 1 = (1111)_2$ . Thus, the 1's complement of a binary number is obtained by subtracting each digit from 1. However, when subtracting binary digits from 1, we can have either 1 - 0 = 1 or 1 - 1 = 0, which causes the bit to change from 0 to 1 from 1 to 0, respectively. Therefore, the 1's complement of a binary number is formed by changing 1's to 0's and 0's to 1's.

Similarly we can obtain simplified results of finding 1's, 7's and 15's complements also discussed later in this section.

#### **1.7.2** Radix Complement or *r*'s Complement

The r's complement of an n-digit number N in base-r is defined as  $r^n - N$  for  $N \neq 0$  and as 0 for N = 0. Comparing with the (r-1)'s complement, we note that the r's complement is obtained by adding 1 to the (r-1)'s complement, since  $r^n - N = [(r^n - 1) - N] + 1$ . Thus, the 10's complement of decimal 8932 is 1067 + 1 = 1068 and is obtained by adding 1 to the 9's complement

Based on above generalized method of finding complements, now we will discuss complements for each number system as follows.

## 1's and 2's Complements

The 1's complement of a binary number is obtained by complementing all its bits, that is, by replacing all 0's by 1's and all 1's by 0's. For example, 1's complement of  $(10010110)_{p}$  is  $(01101001)_{p}$ .

The 2's complement of a binary number is obtained by adding '1' to its 1's complement. The 2's complement of  $(10010110)_2$  is  $(01101010)_2$ .

#### 9's and 10's Complement

Corresponding to the 1's and 2's complement in the binary system, in the decimal number system, we have the 9's complement and 10's complement. The 9's complement of a given decimal number is obtained by subtracting each digit from 9. For example, the 9's complement of  $(2568)_{10}$  would be  $(7431)_{10}$ .

On the other hand, the 10's complement is obtained by adding '1' to 9's complement. For example, the 10's complement of  $(2568)_{10}$  is  $(7432)_{10}$ .

#### 7's and 8's Complement

In the octal number system, we have the 7's and 8's complement. The 7's complement of a given octal number is obtained by subtracting each octal digit from 7. For example, the 7's complement of  $(653)_8$  would be  $(124)_8$ .

The 8's complement is obtained by adding '1' to the 7's complement. For example, the 8's complement of  $(653)_8$  would be  $(125)_8$ .

DO REMEMBER

It is important to note that the complement of the complement results into its original value. To see this relationship, note that the r's complement of N is  $r^n - N$ , so that the complement of the complement is  $r^n - (r^n - N) = N$  and is equal to the original number.

# 15's and 16's Complement

The 15's complement and 16's complement are defined with respect to the hexadecimal number system. The 15's complement is obtained by subtracting each hex digit from 15. For example, the 15's complement of  $(3BF)_{16}$  would be  $(C40)_{16}$ .

The 16's complement is obtained by adding '1' to the 15's complement. For example, the 16's complement of  $(2AE)_{16}$  would be  $(D52)_{16}$ .

**EXAMPLE 1.18**

Find the 1's complement of the following binary numbers.(a) 1101100(b) 0.1011(c) 1101100.1011

#### **SOLUTION :**

(a) Replacing all ones with zeros and all zeros with ones we find that

the 1's complement of 1101100 is 0010011.

(b) Replacing all ones with zeros and all zeros with ones we find that

the 1's complement of 0.1011 is 0.0100.

(c) Replacing all ones with zeros and all zeros with ones we find that

the 1's complement of 1101100.1011 is 0010011.0100

#### READER NOTE

The leading 0 to the left of the binary point that separates the integer and fractional parts remains unchanged.

#### EXAMPLE 1.19

| Find the 2's complement | of the following bina | ary numbers.       |

|-------------------------|-----------------------|--------------------|

| (a) 1101100             | (b) <b>0.1011</b>     | (c) $1101100.1011$ |

#### SOLUTION :

First we find 1's complement of given number and then add 1 to the 1's complement to obtain 2's complement.

(a) 1101100

| Given number :   | $1\ 1\ 0\ 1\ 1\ 0\ 0$ |

|------------------|-----------------------|

| 1's complement : | $0\ 0\ 1\ 0\ 0\ 1\ 1$ |

|                  | + 1                   |

| 2's complement : | 0010100               |

### (b) 0.1011

| 0.1011 |

|--------|

| 0.0100 |

| + 1    |

| 0.0101 |

|        |

(b) 0.8642

| 0.9999  |                               |

|---------|-------------------------------|

| -0.8642 |                               |

| 0.1357  | (9's Complement of $0.8642)$  |

| + 1     | (Add 1)                       |

| 0.1358  | (10's Complement of $0.8642)$ |

(c) 1056.074

| (9's Complement of $1056.074)$  |

|---------------------------------|

| (Add 1)                         |

| (10's Complement of $1056.074)$ |

|                                 |

#### EXAMPLE 1.22

Find the 7's complement of the following octal numbers. (a)  $(407.270)_8$  (b)  $(0156.0037)_8$

# SOLUTION :

(a) We subtract every digit of given number from 7 and we find 7's complement of 407.270 is 370.0507

(b)  $(0156.0037)_8$

$\begin{array}{c} 7 7 7 7 7 7 7 7 7 7 7 7 \\ - 0 1 5 6 . 0 0 3 7 \\ \hline 7 6 2 1 . 7 7 4 0 \end{array}$  (9's Complement of 0156.0037)

# EXAMPLE 1.23

Find the 8's complement of the following octal numbers. (a)  $(346)_8$  (b)  $(217.275)_8$

#### **SOLUTION**:

First we find 7's complement of given number and then add 1 to the 7's complements to obtain the 8's complement.

(a)  $(346)_8$

| 777  |                           |

|------|---------------------------|

| -346 |                           |

| 431  | (7's Complement of $346)$ |

| + 1  | (Add 1)                   |

| 432  | (8's Complement of 346)   |

# (b) $(217.275)_8$

| 777.777  |                               |

|----------|-------------------------------|

| -217.275 |                               |

| 560.502  | (7's Complement of $217.275)$ |

| + 1      | (Add 1)                       |

| 560.503  | (8's Complement of $217.275)$ |

#### EXAMPLE 1.24

Find the 15's complement of the following hexadecimal numbers. (a)  $(A9B)_{16}$  (b)  $(83D.9F)_{16}$

## SOLUTION :

We subtract every digit of the given number from 15 and find the 15's complement.

(a)  $(A9B)_{16}$

(b)  $(83D.9F)_{16}$

|   | 15  | 15 | 15.15 | 15           |                                     |

|---|-----|----|-------|--------------|-------------------------------------|

|   | - 8 | 3  | D.9   | $\mathbf{F}$ |                                     |

| _ | 7   | С  | 2.6   | 0            | • 9's Complement of $(83D.9F)_{16}$ |

#### **EXAMPLE 1.25**

Find the 16's complement of the following hexadecimal numbers. (a)  $(A8C)_{16}$  (b)  $(0070C.B6E)_{16}$

# SOLUTION :

First we find 15's complement of the given number and then add 1 to the 15's complement to obtain the 16's complement. (a)  $(A8C)_{16}$

#### Page 30

numbers. In the 1's complement representation, the positive numbers remain unchanged i.e. positive number are represented in its true binary form. 1's complement representation of negative number can be obtained using following steps:

| METHODOLOGY | Μ | Ε | Т | Н | 0 | D | 0 | L | 0 | G | Υ |

|-------------|---|---|---|---|---|---|---|---|---|---|---|

|-------------|---|---|---|---|---|---|---|---|---|---|---|

- 1. Write the positive number in binary form.

- 2. Find the 1's complement of the binary number.

For example, 1's complement representation of +41 and -41 is shown below

|  | 0 | 1 | 0 | 1 | 0 | 1 | 0 | = +41 |

|--|---|---|---|---|---|---|---|-------|

|--|---|---|---|---|---|---|---|-------|

Sign bit

|  | 1 | 0 | 1 | 0 | 1 | 0 | 1 | = -41 |

|--|---|---|---|---|---|---|---|-------|

|--|---|---|---|---|---|---|---|-------|

Sign bit

The 1's complement of a positive binary number is negative and vice-versa.  $(+8)_{10}$  is represented by  $(00001000)_2$ , whereas  $(11110111)_2$  represents  $(-8)_{10}$  in 1's complement representation of binary number.

#### **1.8.3** 2's Complement Representation

In the 2's complement representation of binary numbers, the MSB represents the sign with a '0' used for a plus sign and a '1' used for a minus sign.

Again, the positive numbers remain unchanged in 2's complement binary form i.e., positive number are represented in its true binary form. 1's complement representation of negative number can be obtained using following steps:

#### METHODOLOGY

- 1. Write the positive sign number.

- 2. Find the 1's complement of the number by replacing 0 by 1 and 1 by 0.

- 3. Find the 2's complement of the number by adding 1 to 1's complement of the number.

For example, 2's complement representation of +41 and -41 is shown below.

|  | 0 | 1 | 0 | 1 | 0 | 1 | 0 | = +41 |

|--|---|---|---|---|---|---|---|-------|

|--|---|---|---|---|---|---|---|-------|

Sign bit

|  | 1 | 0 | 1 | 0 | 1 | 1 | 0 | = -41 |

|--|---|---|---|---|---|---|---|-------|

|--|---|---|---|---|---|---|---|-------|

Sign bit

#### RANGE OF NUMBERS REPRESENTED IN 1'S COMPLEMENT FORM

*n*-bit notation can be used to represent numbers in the range from  $-(2^{n-1}-1)$ to  $+(2^{n-1}-1)$  using the 1's complement format. The eight-bit representation of the 1's complement format can be used to represent decimal numbers in the range from -127 to +127.

# RANGE OF NUMBERS REPRESENTED IN 2'S COMPLEMENT FORM

The *n*-bit notation of the 2's complement representation can be used to represent all decimal numbers in the range from  $-(2^{n-1})$  to  $+(2^{n-1}-1)$

Digital Electronics by Ashish Murolia and RK Kanodia – For More Details visit www.nodia.co.in

$(+25)_{10} = (00011001)_{2}$

Step 3 : Find 1's complement by replacing 0 by 1 and 1 by 0.

1's complement of  $(+25)_{10} = 11100110$

So, 1's complement representation of  $(-25)_{10} = 11100110$

#### (e) 2's complement representation of +25.

Step 1 : Find the binary equivalent of the number.

$(25)_{10} = (0011001)_{2}$

Step 2 : Write the positive number using 8-bits

$(+25)_{10} = (00011001)_{2}$

The 2's complement representation of a positive number is same as the sign magnitude representation of positive number.

Hence, 2's complement representation of  $(+25)_{10} = 00011001$

#### (f) 2's complement representation of -25

Step 1 : Find the binary equivalent of the number

$(25)_{10} = (0011001)_2$

Step 2 : Write the positive number using 8-bits

$(+25)_{10} = (00011001)_{2}$

Step 3 : Find 2's complement of  $(+25)_{10}$

$$(+25)_{10} = 00011001$$

1's complement of  $(+25)_{10} = 1 \ 1 \ 1 \ 0 \ 0 \ 1 \ 1 \ 0$ Add 1 2's complement of  $(+25)_{10} = 1 \ 1 \ 1 \ 0 \ 0 \ 1 \ 1 \ 1$  $= (-25)_{10}$

Hence, 2's complement representation of  $(-25)_{10} = 11100111$

# 1.9 COMPLEMENT BINARY ARITHMETIC

In basic binary arithmetic discussed in section 1.6, we assumed that the numbers are unsigned numbers. The logic of binary arithmetic of unsigned number is not applicable to sign-binary numbers. The sign numbers are represented by 1's complement representation or 2's complement representation and the arithmetic operations are relatively easier to perform using the 1's complement or 2's complement form of signed binary numbers.

#### **1.9.1** Addition using 1's Complement

The addition of sign-numbers can be performed using 1's complement. The methodology for sign-binary number addition using 1's complement is given below. Consider A and B are two sign-numbers.

#### ADVANTAGE OF COMPLEMENT BINARY ARITHMETIC

The advantage of performing subtraction by the complement method is reduction in the hardware. Instead of having separate digital circuits for addition and subtraction, only adding circuits are needed. That is, subtraction is also performed by adders only. Instead of subtracting one number from the other, the complement of the subtrahend is added to the minuend.

# METHODOLOGY

- 1. Obtain the number of bits that are required to represent the sign number. The number of bits required to represent the sign number is n, such that  $2^{n-1}-1$  is greater than or equal to the maximum of the magnitude of A; B; A + B.

- 2. Represent the two numbers to be added in 1's complement form.

- 3. Perform the addition using basic rules of binary arithmetic.

- 4. Check the carry, if the carry is generated, add the carry in LSB position.

- 5. If the MSB of the result is 0, then the answer is positive and in true form. If the MSB of result is 1, then the answer is negative i.e. it is in 1's complement form. So, we have to obtain 1's complement of result to obtain the original number.

The methodology can be best illustrated using the following examples.

## 1. Addition of two positive numbers

8 + 9 = 17

Step 1: Find the number of bits required to represent the number.

$2^{n-1}-1 > \max(8,9,17)$

$2^{n-1}-1 > 17$  and n = 6

Step 2: The 1's complement representation of a positive number is same as its binary equivalent, therefore 1's complement representation of (+8) = 001000

1's complement representation of (+3) = 0010001's complement representation of (+9) = 001001**Step 3:** Binary addition :

The most significant bit is 0, so the sign of the number is positive.

Result =  $(+010001)_{2} = (+17)_{10}$

# 2. Addition of positive and negative number

8 + (-9) = -1

Step 1: Find the number of bits required to represent the number.

$2^{n-1} - 1 > \max(8, 9, 1)$  $2^{n-1} - 1 > 9$  and n = 5

#### **Step 2:**

1's complement representation of (+8) = 010001's complement representation of (-9) = 1's complement of (+9)= 1's complement of (01001) = 10110

# <u>METHODOLOGY</u>

- 1. Obtain the number of bits required to represent the sign number. The number of bits required to represent the sign number is n, such that  $2^{n-1}-1$  is greater than or equal to the maximum of the magnitude of A; B; A - B.

- 2. Obtain the 1's complement of the subtrahend(the number to be subtracted).

- 3. Add A and the 1's complement of the subtrahend.

- 4. Check the carry, if the carry is generated, add the carry in LSB position.

- 5. If the MSB of result is 0, then the answer is positive and in true form. If the MSB of result is 1, then the answer is negative i.e. it is in 1's complement form. So, we have to obtain 1's complement of result to obtain the original number

(i) 8-9 = -1

8-9=8+1's complement of 9.

Step 1: Find the number of bits required to represent the number.

$2^{n-1} - 1 > \max(8,9,1)$  $2^{n-1} - 1 > 9$  and n = 5

#### **Step 2:**

1's complement of (+9) = 1's complement of (01001)

= 10110

Step 3: Binary addition

$\begin{array}{ccccccc}

0 & 1 & 0 & 0 & 0 & \bullet & A \\

+ & 1 & 0 & 1 & 1 & 0 & \\

\hline

& & 1 & 1 & 1 & 1 & 0 & \\

\end{array} \bullet 1's \text{ complement of } B$

The most significant bit is 1, the answer is negative, and it is in 1's complement form.

Result = -(1's complement of 11110) =  $-(00001)_2 = (-1)_{10}$

(ii) 9 - 8 = 1

9-8=9+1's complement of 8

Step 1: Find the number of bits required to represent the number.

$2^{n-1} - 1 > \max(8,9,1)$  $2^{n-1} - 1 > 9$  and n = 5

#### **Step 2:**

1's complement representation of (+9) = 010011's complement of (-8) = 1's complement of (+8)= 1's complement of (01000)= 10111

#### **READER NOTE**

The number to be subtracted is referred to as subtrahend and the number from which it is subtracted is referred to as minuend.

Chapter 1

**Step 3:** Binary addition :

| $0\ 1\ 0\ 0\ 1$ | • A                     |

|-----------------|-------------------------|

| + 1 0 1 1 1     | • 1's complement of $B$ |

| $1 \ 1 \ 1 \ 1$ | • Carry                 |

| 100000          | _                       |

| 1               | • Carry is added        |

| 00001           |                         |

The most significant bit is 0, the answer is positive, and it is true form.

Result =

$$(00001)_2 = (1)_{10}$$

# 1.9.3 Addition using 2's Complement

The 2's complement is the most commonly used code for processing positive and negative binary numbers. It forms the basis of arithmetic circuits in modern computers. The addition of sign-binary numbers takes place using 2's complement.

The methodology for sign binary number addition using 2's complement is given below. Consider A and B are two sign numbers.

# METHODOLOGY

| 1. | Find the number of bits required to represent the sign            |

|----|-------------------------------------------------------------------|

|    | number. The number of bits required to represent the sign         |

|    | number is $n$ , such that $2^{n-1}-1$ is greater than or equal to |

|    | the maximum of the magnitude of $A$ ; $B$ ; $A + B$               |

|    |                                                                   |

- 2. Represent the two numbers two be added in 2's complement form.

- 3. Do the binary addition using binary arithmetic.

- 4. Ignore the carry, if it is generated.

- 5. If the MSB is 0, then the answer is positive i.e., it is in true form. If MSB of the result is 1, then the answer is negative i.e., it is in 2's complement form. So, we have to obtain 2's complement of this result to get final answer.

# 1. Addition of Two Positive Numbers

8 + 9 = 17

Step 1: Find the number of bits required to represent the number.

$$2^{n-1} - 1 > \max(8,9,17)$$

$2^{n-1} - 1 > 17$  and  $n = 6$

# **Step 2:**

2's complement representation of (+8) = 0010002's complement representation of (+9) = 001001

${\bf Step \ 3: \ Binary \ addition:}$

Page 38

$$= 110110 + 1 = 110111$$

Step 4: Binary addition:

$\begin{array}{cccc} 1 & 1 & 1 & 0 & 0 & \bullet & A \\ \hline + 1 & 1 & 0 & 1 & 1 & 1 \\ \hline \hline 1 & 0 & 1 & 1 & 1 & 1 & \bullet & B \\ \hline \end{array} \bullet B & \bullet & \text{Ignore the carry} \end{array}$

The most significant bit is 1, the answer is negative; and it is in 2's complement form.

Result = -2's complement of (101111) = -1's complement (101111) + 1 = -(010000) + 1=  $-(010001)_2 = (-17)_{10}$

### 1.9.4 Subtraction using 2's Complement

Subtraction is similar to addition. The subtraction of a binary number B from another binary number A is equivalent to the addition of the 2's complement of B with A, i.e. (A - B) = A + 2's complement of B.

The methodology for binary subtraction using 2's complement is as follows:

# METHODOLOGY

- 1. Find the number of bits required to represent the sign number. The number of bits required to represent the sign-binary number is n, such that  $2^{n-1}-1$  is greater than or equal to the maximum of the magnitude of A; B; A B.

- 2. Represent the subtrahend in 2's complement form.

- 3. Add the 2's complement of subtrahend to the minuend.

- 4. Ignore the carry, if it is generated.

- 5. If the MSB is 0, then the answer is positive i.e., it is in true form. If MSB of the result is 1, then the answer is negative i.e., it is in 2's complement form. So, we have to obtain 2's complement of this result to get final answer.

We consider the following example for a better understanding of the above process.

(i) 8 - 9 = -1

8-9=8+2's complement of 9

Step 1: Find the number of bits required to represent the number.

$2^{n-1} - 1 > \max(8,9,1)$  $2^{n-1} - 1 > 9$  and n = 5

### **Step 2**:

2's complement representation of (-9) = 2's complement of (+9)= 1's complement of (+9) + 1= 1's complement of (001001) + 1= 110110 + 1 = 110111  $\begin{array}{ccccccc}

0 & 1 & 0 & 0 & 0 \\

+1 & 0 & 1 & 1 & 1 \\

\hline

1 & 1 & 1 & 1 & 1

\end{array} \bullet A$ • 2's complement of B

The most significant bit is 1, the answer is negative, and it is in 2's complement form.

> Result = - 2's complement of (11111) = - 1's complement of (11111) + 1 = -(00000) + 1 = -(00001)\_2 = (-1)\_{10} = -1 = 1

(ii) 9 - 8 = 1

9-8=9+1's complement of 8

Step 1: Find the number of bits required to represent the number.

$2^{n-1} - 1 > \max(8,9,1)$  $2^{n-1} - 1 > 9$  and n = 5

**Step 2:**

2's complement representation of (-8) = 2's complement of (+8)

= 1's complement of (+8) + 1= 1's complement of (001000) + 1= 110111 + 1 = 111000

Step 4: Binary addition

$\begin{array}{cccc}

0 & 1 & 0 & 0 & 1 & \bullet & A \\

+ & 1 & 1 & 0 & 0 & 0 & 0 \\

\hline

1 & & \bullet & \text{Carry} \\

\hline

\hline

1 & & \bullet & \text{Ignore the carry} & \bullet & \text{Ignore the carry} \\

\end{array}$

The MSB is 0, the answer is positive, and it is in true form.

Result

$$= (00001) = 1$$

**EXAMPLE 1.27**

Perform the following arithmetic operations by using 1's complement method. (a) 25 + 14 (b) 28 - 15(c) 20 - 42 (d) -42 - 20

# **SOLUTION** :

(a) 25 + 14 = 39

Step 1: Find the number of bits required to represent the number.

$$2^{n-1} - 1 > \max(25, 14, 39)$$

$2^{n-1} - 1 > 39, n = 7$

Chapter 1

(d) -42 - 20 = -62

Step 1: Find the number of bits required to represent the number.

$2^{n-1} - 1 > \max(42, 20, 62)$

$2^{n-1} - 1 > 62$  and n = 7

Step 2: 1's complement representation of (-42) = 1's complement of (+42)

= 1's complement of (0101010)= 1010101

1's complement representation of (-20) = 1's complement of (+20)

= 1's complement of (0010100)

= 1101011

Step 3: Binary addition :

| -42 | $1 \ 0 \ 1 \ 0 \ 1 \ 0 \ 1$ | • 1's complement of $A$         |

|-----|-----------------------------|---------------------------------|

| -20 | + 1 1 0 1 0 1 1             | $\bullet$ 1's complement of $B$ |

| -62 | $1\ 1\ 1\ 1\ 1\ 1$          | • Carry                         |

|     | 11000000                    |                                 |

|     | + 1                         | • Add carry                     |

|     | $1 \ 0 \ 0 \ 0 \ 0 \ 1$     |                                 |

|     |                             |                                 |

The MSB is 1, the answer is negative, and it is 1's complement form.

Result = -1's complement of (1000001) = -(0111110)= -62

#### **EXAMPLE 1.28**

Perform the following arithmetic operations by using 2's complement methods. (a) 76 + 12 (b) 56 - 27(c) 21 - 42 (d) -46 - 25

#### SOLUTION :

(a) 76 + 12 = 88

Step 1: Find the number of bits required to represent the number.

$2^{n-1} - 1 > \max(76, 12, 88)$

$2^{n-1} - 1 > 88, \ n = 8$

**Step 2:** 2's complement representation of positive number is same as its binary form.

$(76)_{10} = (01001100)_2$  $(12)_{10} = (00001100)_2$  Step 3: Binary Addition

| 76    | $0\ 1\ 0\ 0\ 1\ 1\ 0\ 0$            | $\bullet A$     |

|-------|-------------------------------------|-----------------|

| + 1 2 | $+ \ 0 \ 0 \ 0 \ 0 \ 1 \ 1 \ 0 \ 0$ | • B             |

| 88    | 11                                  | $\bullet$ Carry |

|       | 01011000                            |                 |

There is no carry and MSB is 0. So, the result is positive.

Result

$$=+(01011000) = (+88)_{10}$$

(b) 56 - 27 = 29

**Binary Equivalents**

$$(56)_{10} = (111000)_2 (27)_{10} = (011011)_2$$

Step 1: Find the number of bits required to represent the number.

$$2^{n-1} - 1 > \max(56, 27, 29)$$

$2^{n-1} - 1 > 56, n = 7$

So, binary equivalents are

$$A = (56)_{10} = (0111000)_2$$

$$B = (27)_{10} = (0011011)_2$$

# **Step 2:**

2's complement of  $(+27)_{10}$

$\begin{array}{cccc} 0 & 0 & 1 & 1 & 0 & 1 & 1 \\ 1 & 1 & 0 & 0 & 1 & 0 & 0 \\ \hline & & + & 1 \\ \hline & & 1 & 1 & 0 & 0 & 1 & 0 & 1 \end{array} \quad \bullet \text{ 2's complement of } B$

Step 3: Binary Addition

There is carry, ignore it. The MSB is 0. So, the result is positive and is in normal binary form.

(c) 21 - 42 = -21

21 - 42 = 21 + 2's complement of 42 Step 1: Find the number of bits required to represent the number.

$$2^{n-1} - 1 > \max(21, 42, 21)$$

$2^{n-1} - 1 > 42$  and n = 7

Step 2: 1's complement of (+42)

The MSB is 1, the answer is negative and it is in 2's complement form.

Result = -2's complement of (10111001) = -(01000111) = -71

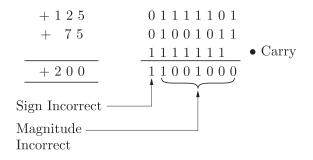

#### 1.10 ARITHMETIC OVERFLOW

When we add two numbers and the number of bits required to represent the sum exceeds the number of bits in the two numbers, it is known as overflow result. This overflow condition can occur only when two positive or two negative are being added, and it always produces an incorrect result. Overflow can be detected by checking to see that the sign bit of the result is the same as the sign bits of the numbers being added.

For illustration, we consider the sum of two positive binary numbers as Case 1 and the sum of two negative binary numbers as Case 2.

#### Case 1 : Sum of two positive numbers

Consider the sum of +125 and +75

As the decimal sum of +125 and +75 is +200; the length of the number is 8-bit, the result is 9-bit and an overflow occurs. This overflow changes the sign of the result and the answer is wrong. Result shows that the sum of two positive numbers is negative, which is wrong.

#### Case 2 : Sum of two negative numbers

Consider the sum of -61 and -43

| -61  | $1 \ 0 \ 1 \ 1 \ 1 \ 1 \ 0 \ 1$     |         |

|------|-------------------------------------|---------|

| -4.3 | $1 \ 0 \ 1 \ 0 \ 1 \ 0 \ 1 \ 1$     |         |

|      | 111111                              | • Carry |

| -104 | $1 \ 0 \ 1 \ 1 \ 0 \ 1 \ 0 \ 0 \ 0$ |         |

As the decimal sum of -61 and -43 is -104, the length of the number is 8-bit, the result is 9-bit and an overflow occurs.

#### Chapter 1

### 1.11 HEXADECIMAL ARITHMETIC

The rules of arithmetic operation in hexadecimal number system are same as in binary and decimal systems. But, we are not interested in performing hexadecimal arithmetic operation using hexadecimal representation of numbers. The better way to perform arithmetic operation of hexadecimal numbers is using 1's or 2's complement and other is using 15's and 16's complement, discussed as follows.

#### 1.11.1 Hexadecimal Arithmetic using 1's or 2's Complements

In this method first we convert the hexadecimal numbers into equivalent binary numbers and then addition and subtraction can be performed using 1's or 2's complement as discussed earlier in section 1.9. Then, convert the result to hexadecimal again.

#### **EXAMPLE 1.29**

Perform the following arithmetic operation using 2's complement method.

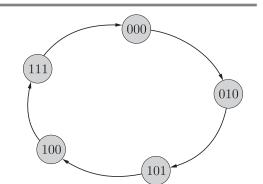

| (a) $(6E)_{16} + (C5)_{16}$ | (b) $(C4)_{16} - (7B)_{16}$     |